# MIPS R4000 Microprocessor User's Manual

Second Edition

Joe Heinrich

© 1994 MIPS Technologies, Inc. All Rights Reserved.

#### **RESTRICTED RIGHTS LEGEND**

Use, duplication, or disclosure of the technical data contained in this document by the Government is subject to restrictions as set forth in subdivision (c) (1) (ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and/or in similar or successor clauses in the FAR, or in the DOD or NASA FAR Supplement. Unpublished rights reserved under the Copyright Laws of the United States. Contractor/manufacturer is MIPS Technologies, Inc., 2011 N. Shoreline Blvd., Mountain View, CA 94039-7311.

RISCompiler, RISC/os, R2000, R6000, R4000, and R4400 are trademarks of MIPS Technologies, Inc. MIPS and R3000 are registered trademarks of MIPS Technologies, Inc.

IBM 370 is a registered trademark of International Business Machines.

VAX is a registered trademark of Digital Equipment Corporation.

iAPX is a registered trademark of Intel Corporation.

MC68000 is a registered trademark of Motorola Inc.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company, Ltd.

MIPS Technologies, Inc. 2011 North Shoreline Mountain View, California 94039-7311

### Acknowledgments for the First Edition

First of all, special thanks go to **Duk Chun** for his patient help in supplying and verifying the content of this manual; that this manual is technically correct is, in a very large part, directly attributable to him.

Thanks also to the following people for supplying portions of this book: **Shabbir Latif**, for, among other things, the exception handler flow charts, the description of the output buffer edge-control logic, and the interrupts; once again, **Duk Chun**, for his paper on R4000 processor synchronization support; **Paul Ries**, for confirming the accuracy of sections describing the memory management and the caches; **John Mashey**, for verifying the R4000 processor actually *does* employ the 64-bit architecture; **Dave Ditzel**, for raising the issue in the first place; and **Mike Gupta**, for substantiating various aspects of the errata. Finally, thanks to **Ed Reidenbach** for supplying a large portion of the parity and ECC sections of this manual, and **Michael Ngo** for checking their accuracy.

Thanks also to the following folks for their technical assistance: Andy Keane, Keith Garrett, Viggy Mokkarala, Charles Price, Ali Moayedian, George Hsieh, Peter Fu, Stephen Przybylski, Michael Woodacre, and Earl Killian. Also to be thanked are the people at *fvn@world.std.com*: Bill Tuthill, Barry Shein, Bob Devine, and Alan Marr, for helping place RISC in a pecuniary perspective. Also, thanks to the following people at the *mystery\_train@swim2birds* news group: *toma*, *dan\_sears*, *jharris@garnet*, *tut@cairo* (again), and *elvis@dalkey(mateo\_b)*. Their nightfor-day netversations, fueled by caffeine, concerning the viability of the cyberpsykinetic compute-core model helped form an important basis of this book.

On the editorial front, thanks once again to **Ms. Robin Cowan**, of the *Consortium of Editorial Arts* for her labors in editing this manual. Thanks to **Evelyn Spire** for slaving over that bottomless black well we refer to as an "Index." Thanks also, once again, to **Karen Gettman**, and **Lisa Iarkowski** at Prentice-Hall for their help.

On the artistic side, thanks to **Jeanne Simonian**, of the Creative department here at Silicon Graphics, for the book cover design; and thanks to **Pam Flanders** for providing MarCom tactical support.

Have we missed anyone? If so, here is where we apologize for doing so.

Joe Heinrich April 1, 1993 Mt. View, California

### Acknowledgments for the Second Edition

Thanks go to **Shabbir Latif**, from whose errata the major part of this second edition is derived. Thanks also to **Charlie Price** for, among other things, making available his revision of the ISA.

On the production side, thanks to **Kay Maitz**, **Beth Fraker**, **Molly Castor**, **Lynnea Humphries**, and **Claudia Lohnes** for their assistance at the center of the hurricane.

Joe Heinrich joeh@sgi.com April 1, 1994 Mt. View, California

## Preface

This book describes the MIPS R4000 and R4400 family of RISC microprocessors (also referred to in this book as *processor*).

#### **Overview of the Contents**

**Chapter 1** is a discussion (including the historical context) of RISC development in general, and the R4000 microprocessor in particular.

Chapter 2 is an overview of the CPU instruction set.

**Chapter 3** describes the operation of the R4000 instruction execution pipeline, including the basic operation of the pipeline and interruptions that are caused by interlocks and exceptions.

**Chapter 4** describes the memory management system including address mapping and address spaces, virtual memory, the translation lookaside buffer (TLB), and the System Control Processor (CP0).

**Chapter 5** describes the exception processing resources of R4000 processor. It includes an overview of the CPU exception handling process and describes the format and use of each CPU exception handling register.

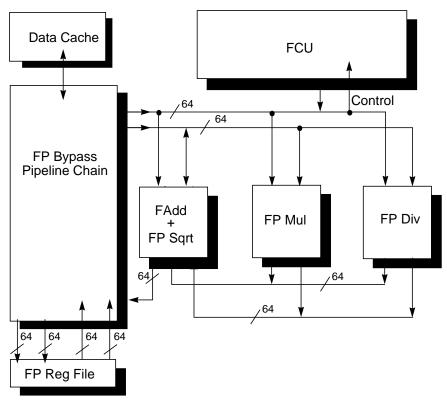

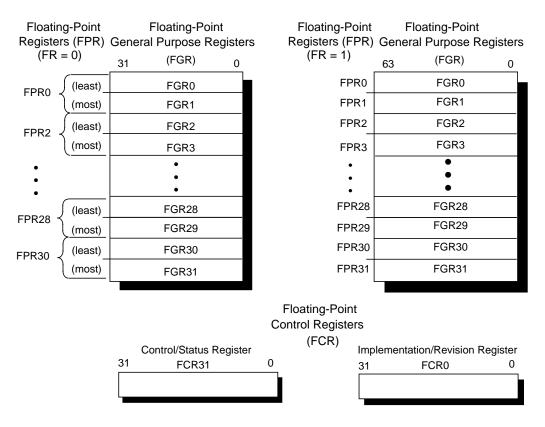

**Chapter 6** describes the Floating-Point Unit (FPU), a coprocessor for the CPU that extends the CPU instruction set to perform floating-point arithmetic operations. This chapter lists the FPU registers and instructions.

Chapter 7 describes the FPU exception processing.

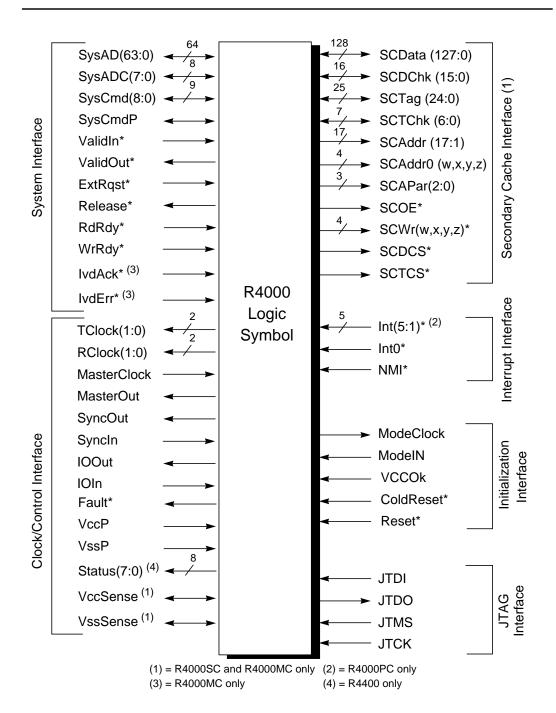

**Chapter 8** describes the signals that pass between the R4000 processor and other components in a system. The signals discussed include the System interface, the Clock/Control interface, the Secondary Cache interface, the Interrupt interface, the Initialization interface, and the JTAG interface.

**Chapter 9** describes in more detail the Initialization interface, which includes the boot modes for the processor, as well as system resets.

**Chapter 10** describes the clocks used in the R4000 processor, as well as the processor status reporting mechanism.

**Chapter 11** discusses cache memory, including the operation of the primary and secondary caches, and cache coherency in a multiprocessor system.

**Chapter 12** describes the System interface, which allows the processor access to external resources such as memory and input/output (I/O). It also allows an external agent access to the internal resources of the processor, such as the secondary cache.

**Chapter 13** describes the Secondary Cache interface, including read and write cycle timing. This chapter also discusses the interface buses and signals.

**Chapter 14** describes the Joint Test Action Group (JTAG) interface. The JTAG boundary scan mechanism tests the interconnections between the R4000 processor, the printed circuit board to which it is mounted, and other components on the board.

**Chapter 15** describes the single nonmaskable processor interrupt, along with the six hardware and two software processor interrupts.

**Chapter 16** describes the error checking and correcting (ECC) mechanisms of the R4000 processor.

**Appendix A** describes the R4000 CPU instructions, in both 32- and 64bit modes. The instruction list is given in alphabetical order.

**Appendix B** describes the R4000 FPU instructions, listed alphabetically.

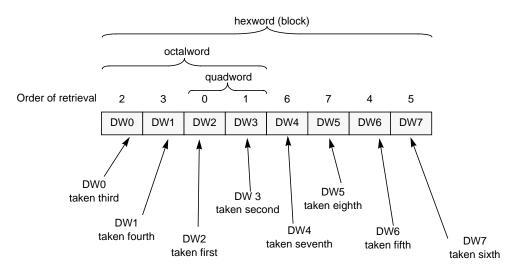

**Appendix C** describes sub-block ordering, a nonsequential method of retrieving data.

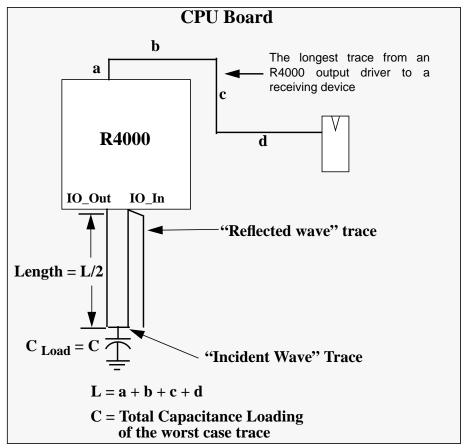

**Appendix D** describes the output buffer and the  $\Delta i/\Delta t$  control mechanism.

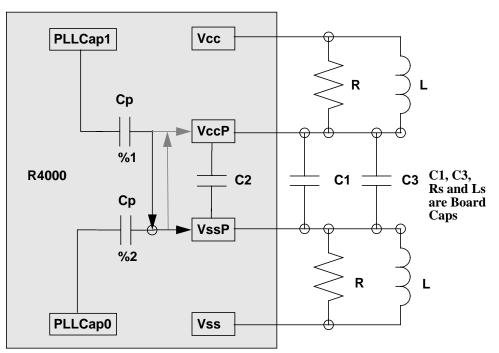

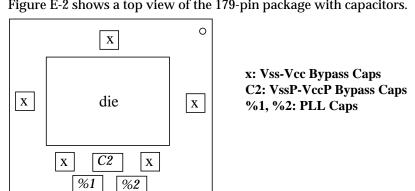

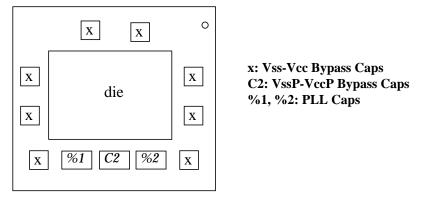

**Appendix E** describes the passive components that make up the phase-locked loop (PLL).

Appendix F describes Coprocessor 0 hazards.

Appendix G describes the R4000 pinout.

#### A Note on Style

I

A brief note on some of the stylistic conventions used in this book: bits, fields, and registers of interest from a software perspective are italicized (such as *Config* register); signal names of more importance from a hardware point of view are rendered in bold (such as **Reset**\*).

A range of bits uses a colon as a separator; for instance, **(15:0)** represents the 16-bit range that runs from bit 0, inclusive, through bit 15. (In some places an ellipsis may used in place of the colon for visibility: **(15...0)**.)

Preface

## Preface to the Second Edition

#### **Changes From the First Edition**

The second edition of this book incorporates certain low-level changes and technical additions, but retains a substantive identity with the original version.

Changes from the first edition are indicated by left-margin vertical rules.

#### **Getting MIPS Documents On-Line**

MIPS documents (including an electronic version of the errata) are available on-line, through the file transport protocol (FTP). To retrieve them, follow the steps below. The text you are to type is shown in **Courier Bold** font; the computer's responses are in shown in Courier Regular font.

1. First, place yourself in the directory on your system within which you want to store the retrieved files. Do this by typing:

cd <directory\_you\_want\_file\_to\_be\_in>

2. Access the MIPS document server, **sgigate**, through FTP by typing:

#### ftp sgigate.sgi.com

3. The server tells you when you are connected for FTP by responding:

Connected to sgigate.sgi.com.

Preface

| Next (after some announcements) the server asks you to log in by requesting a name and then a password.                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name (sgigate.sgi.com: <login_name>):</login_name>                                                                                                                                                       |

| Login by typing <b>anonymous</b> for your name and your <b>electronic mail address</b> for your password.                                                                                                |

| Name (sgigate.sgi.com: <login_name>): anonymous</login_name>                                                                                                                                             |

| 331 Guest login ok, type your name as password.                                                                                                                                                          |

| Password: your_email_address                                                                                                                                                                             |

| The system indicates you have successfully logged in by supplying an FTP prompt:                                                                                                                         |

| ftp>                                                                                                                                                                                                     |

| Go to the pub/doc directory by typing:                                                                                                                                                                   |

| ftp> cd pub/doc                                                                                                                                                                                          |

| You can take a look at the contents of the <b>doc</b> directory by listing them:                                                                                                                         |

| ftp> <b>1s</b>                                                                                                                                                                                           |

| You will find several R4000-related subdirectories, such as R4200, R4400, and R4600. When you find the subdirectory you want, <b>cd</b> into that subdirectory and retrieve the file you want by typing: |

| get <filename></filename>                                                                                                                                                                                |

| This copies the file from sgigate back to your system.                                                                                                                                                   |

| When you have retrieved the files you want, exit from <b>ftp</b> by typing:                                                                                                                              |

| ftp> quit                                                                                                                                                                                                |

| If the file was encoded for transmission, you must decode it, after retrieval, by typing:                                                                                                                |

| uudecode <filename></filename>                                                                                                                                                                           |

| If the file was compressed for transmission, you must uncompress<br>it, after retrieval, by typing:                                                                                                      |

| uncompress <filename></filename>                                                                                                                                                                         |

| If you tarred the file, type:                                                                                                                                                                            |

| tar xvof <filename></filename>                                                                                                                                                                           |

|                                                                                                                                                                                                          |

## Table of Contents

### Preface

| Overview of the Contents | . vii |

|--------------------------|-------|

| A Note on Style          | . ix  |

### Preface to the Second Edition

| Changes From the First Edition xi | i |

|-----------------------------------|---|

| Getting MIPS Documents On-Linex   | ί |

Table of Contents

### 1

### Introduction

| Benefits of RISC Design                | 2  |

|----------------------------------------|----|

| Shorter Design Cycle                   | 3  |

| Effective Utilization of Chip Area     | 3  |

| User (Programmer) Benefits             | 3  |

| Advanced Semiconductor Technologies    | 3  |

| Optimizing Compilers                   | 4  |

| MIPS RISCompiler Language Suite        | 5  |

| Compatibility                          | 6  |

| Processor General Features             | 6  |

| R4000 Processor Configurations         | 7  |

| R4400 Processor Enhancements           | 7  |

| R4000 Processor                        | 9  |

| 64-bit Architecture                    | 9  |

| Superpipeline Architecture             | 11 |

| System Interface                       | 11 |

| CPU Register Overview                  | 12 |

| CPU Instruction Set Overview           | 14 |

| Data Formats and Addressing            | 24 |

| Coprocessors (CP0-CP2)                 | 27 |

| System Control Coprocessor, CP0        | 27 |

| Floating-Point Unit (FPU), CP1         | 30 |

| Memory Management System (MMU)         | 31 |

| The Translation Lookaside Buffer (TLB) | 31 |

| Operating Modes                        | 32 |

| Cache Memory Hierarchy                 | 32 |

| Primary Caches                         | 33 |

| Secondary Cache Interface              | 33 |

MIPS R4000 Microprocessor User's Manual

### **CPU Instruction Set Summary**

| CPU Instruction Formats                           |    |

|---------------------------------------------------|----|

| Load and Store Instructions                       |    |

| Scheduling a Load Delay Slot                      |    |

| Defining Access Types                             |    |

| Computational Instructions                        |    |

| 64-bit Operations                                 |    |

| Cycle Timing for Multiply and Divide Instructions |    |

| Jump and Branch Instructions                      | 41 |

| Overview of Jump Instructions                     | 41 |

| Overview of Branch Instructions                   |    |

| Special Instructions                              |    |

| Exception Instructions                            |    |

| Coprocessor Instructions                          |    |

|                                                   |    |

### 3

2

### The CPU Pipeline

| CPU Pipeline Operation                             | 44 |

|----------------------------------------------------|----|

| CPU Pipeline Stages                                | 45 |

| Branch Delay                                       | 48 |

| Load Delay                                         | 48 |

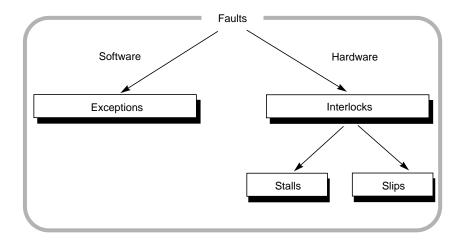

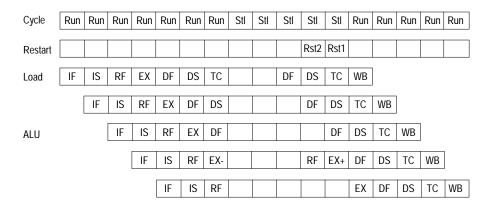

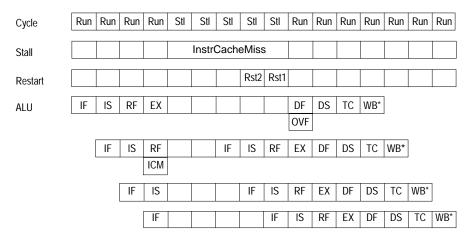

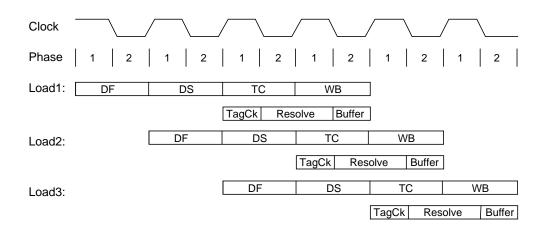

| Interlock and Exception Handling                   | 49 |

| Exception Conditions                               | 52 |

| Stall Conditions                                   | 53 |

| Slip Conditions                                    | 53 |

| External Stalls                                    |    |

| Interlock and Exception Timing                     | 53 |

| Backing Up the Pipeline                            |    |

| Aborting an Instruction Subsequent to an Interlock |    |

| Pipelining the Exception Handling                  |    |

| Special Cases                                      |    |

| Performance Considerations                         |    |

| Correctness Considerations                         | 58 |

| R4400 Processor Uncached Store Buffer              |    |

|                                                    |    |

#### 4

## Memory Management

| Translation Lookaside Buffer (TLB)                 | 62 |

|----------------------------------------------------|----|

| Hits and Misses                                    | 62 |

| Multiple Matches                                   | 62 |

| Address Spaces                                     | 63 |

| Virtual Address Space                              | 63 |

| Physical Address Space                             | 64 |

| Virtual-to-Physical Address Translation            | 64 |

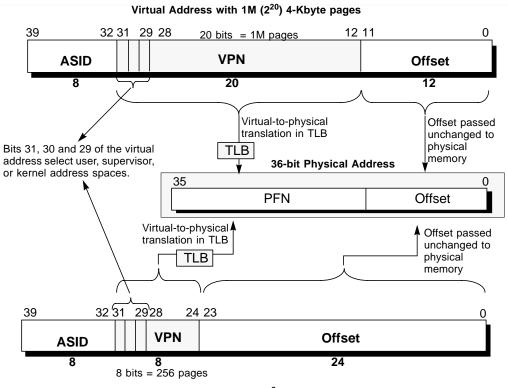

| 32-bit Mode Address Translation                    | 65 |

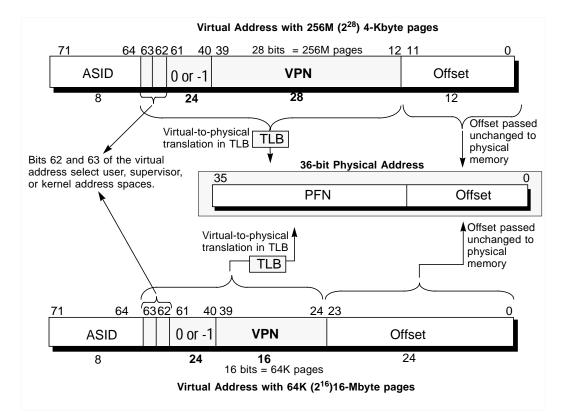

| 64-bit Mode Address Translation                    | 66 |

| Operating Modes                                    | 67 |

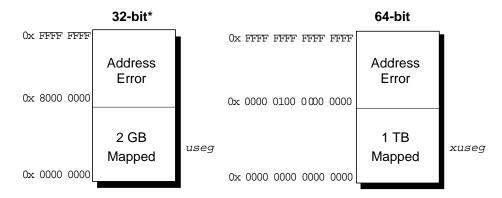

| User Mode Operations                               | 67 |

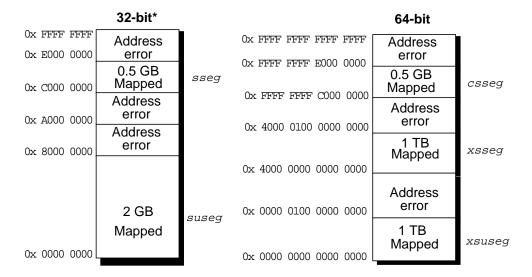

| Supervisor Mode Operations                         | 69 |

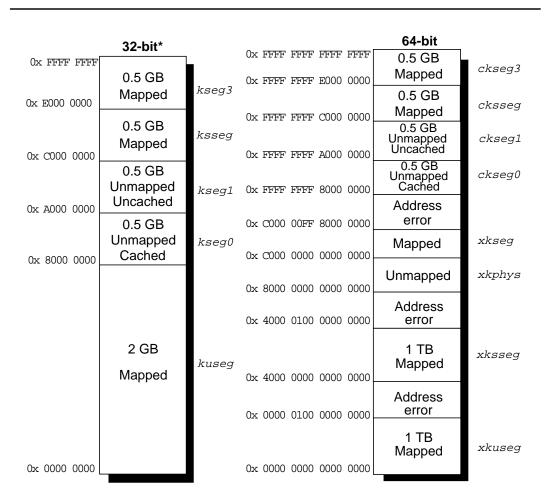

| Kernel Mode Operations                             | 73 |

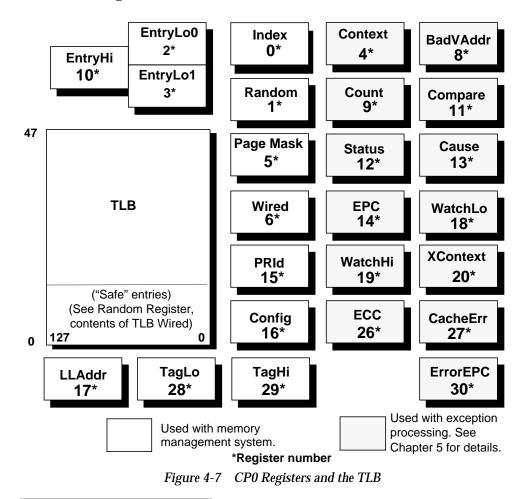

| System Control Coprocessor                         | 80 |

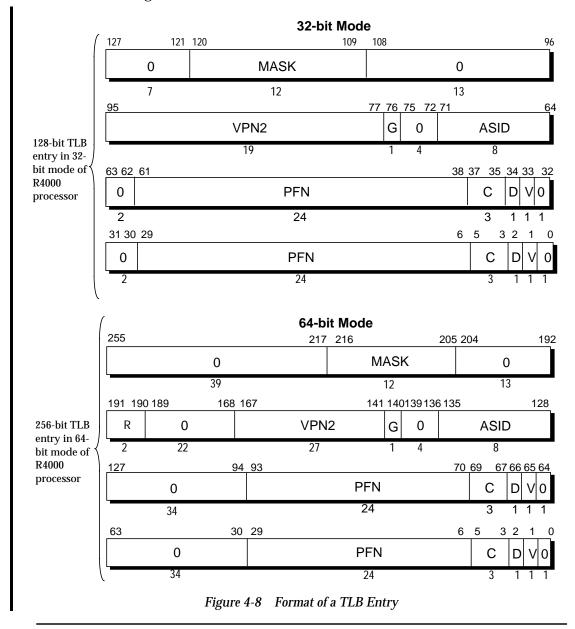

| Format of a TLB Entry                              | 81 |

| CP0 Registers                                      | 84 |

| Index Register (0)                                 | 85 |

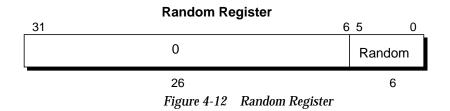

| Random Register (1)                                | 86 |

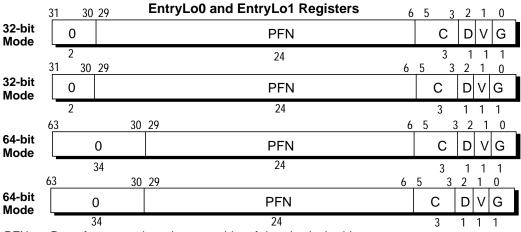

| EntryLo0 (2), and EntryLo1 (3) Registers           | 87 |

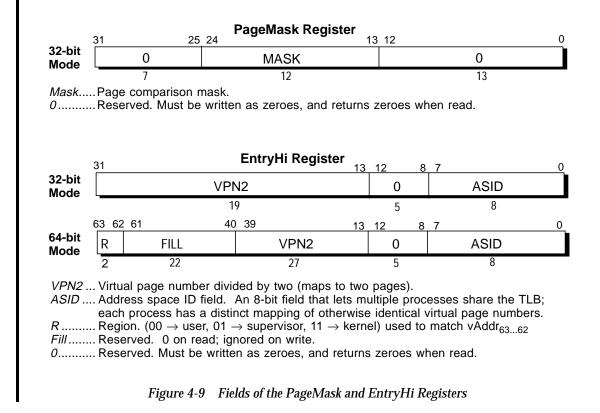

| PageMask Register (5)                              | 87 |

| Wired Register (6)                                 | 88 |

| EntryHi Register (CP0 Register 10)                 | 89 |

| Processor Revision Identifier (PRId) Register (15) | 89 |

| Config Register (16)                               | 90 |

| Load Linked Address (LLAddr) Register (17)         | 93 |

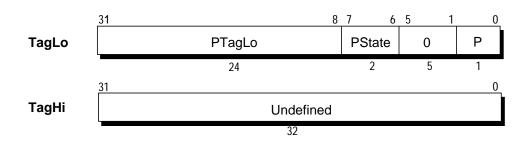

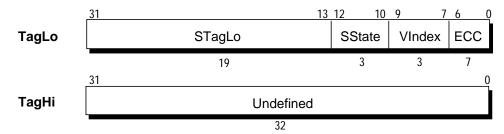

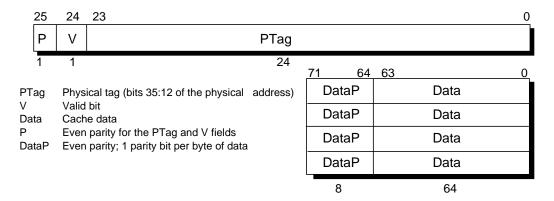

| Cache Tag Registers [TagLo (28) and TagHi (29)]    | 93 |

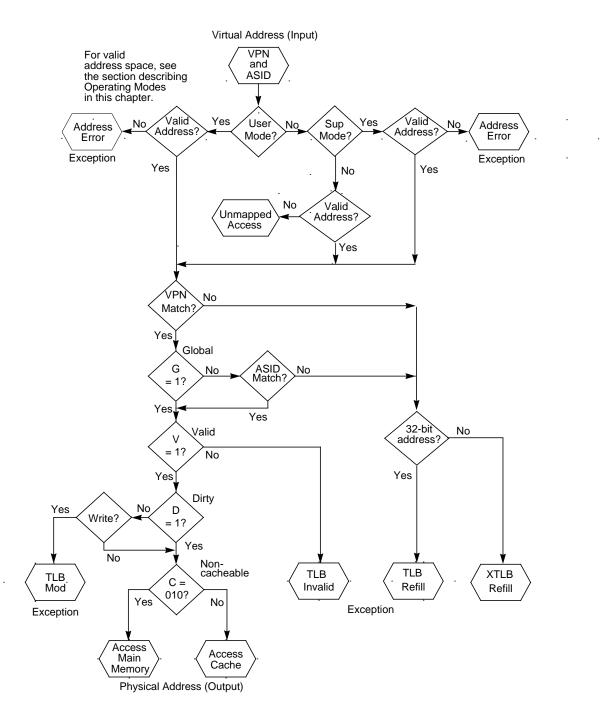

| Virtual-to-Physical Address Translation Process    |    |

| TLB Misses                                         |    |

| TLB Instructions                                   | 97 |

|                                                    |    |

## 5

## **CPU Exception Processing**

| How Exception Processing Works                            | 100 |

|-----------------------------------------------------------|-----|

| Exception Processing Registers                            |     |

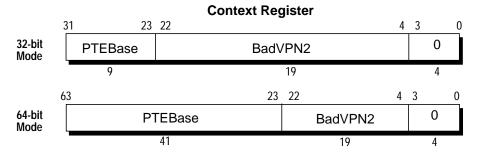

| Context Register (4)                                      | 102 |

| Bad Virtual Address Register (BadVAddr) (8)               | 103 |

| Count Register (9)                                        | 103 |

| Compare Register (11)                                     | 104 |

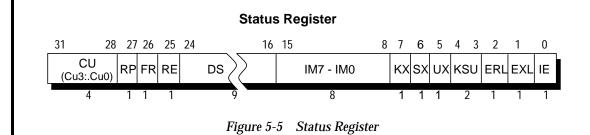

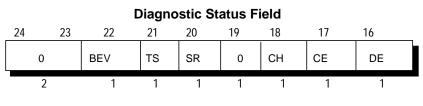

| Status Register (12)                                      | 105 |

| Status Register Format                                    | 105 |

| Status Register Modes and Access States                   | 109 |

| Status Register Reset                                     | 110 |

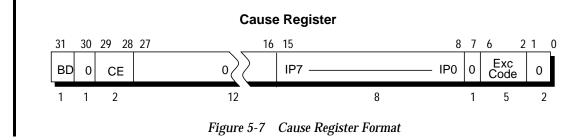

| Cause Register (13)                                       | 110 |

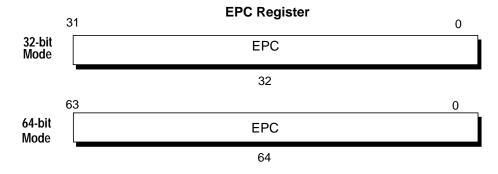

| Exception Program Counter (EPC) Register (14)             | 112 |

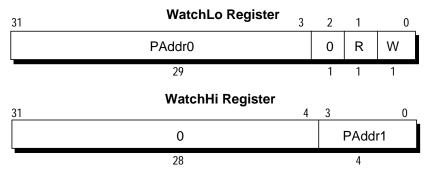

| WatchLo (18) and WatchHi (19) Registers                   | 113 |

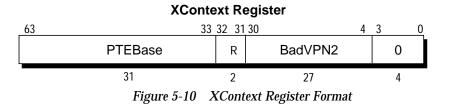

| XContext Register (20)                                    | 114 |

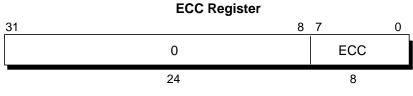

| Error Checking and Correcting (ECC) Register (26)         | 115 |

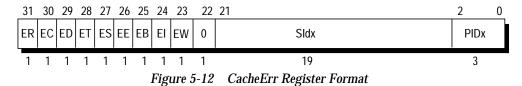

| Cache Error (CacheErr) Register (27)                      | 116 |

| Error Exception Program Counter (Error EPC) Register (30) | 118 |

| Processor Exceptions                                      | 119 |

| Exception Types                                           | 119 |

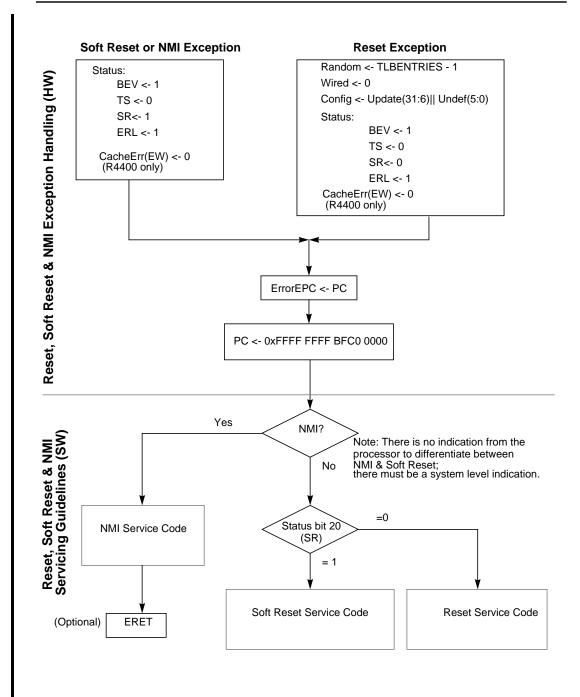

| Reset Exception Process                                   | 120 |

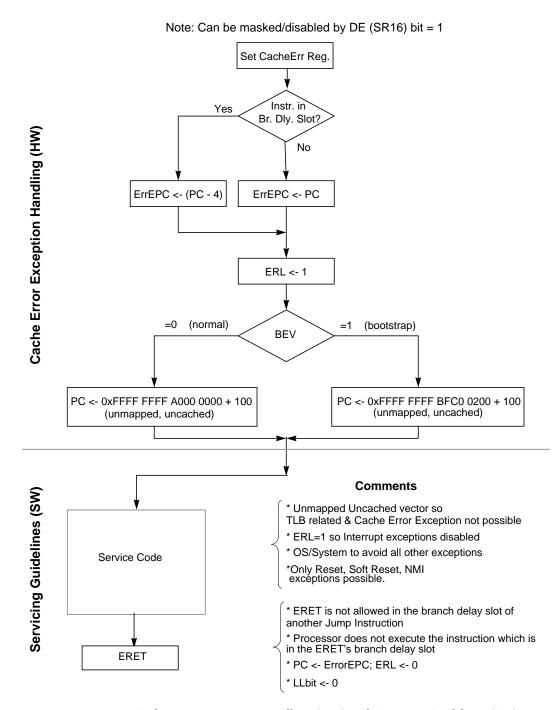

| Cache Error Exception Process                             | 120 |

| Soft Reset and NMI Exception Process                      | 121 |

| General Exception Process                                 | 121 |

| Exception Vector Locations                                | 122 |

| Priority of Exceptions                                    | 123 |

| Reset Exception                                           | 124 |

| Soft Reset Exception                                      | 125 |

| Address Error Exception                                   | 127 |

| TLB Exceptions                                            | 128 |

| TLB Refill Exception                                      | 129 |

| TLB Invalid Exception                                     | 130 |

| TLB Modified Exception                                    | 131 |

| Cache Error Exception                                     | 132 |

| Virtual Coherency Exception                               | 133 |

| Bus Error Exception                                       | 134 |

| Integer Overflow Exception                                | 135 |

|                                                           |     |

MIPS R4000 Microprocessor User's Manual

#### Table of Contents

| Trap Exception                              | 136 |

|---------------------------------------------|-----|

| System Call Exception                       | 137 |

| Breakpoint Exception                        | 138 |

| Reserved Instruction Exception              | 139 |

| Coprocessor Unusable Exception              | 140 |

| Floating-Point Exception                    | 141 |

| Watch Exception                             | 142 |

| Interrupt Exception                         | 143 |

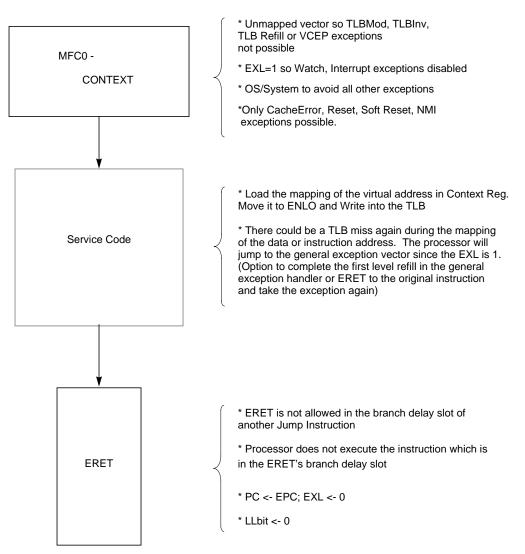

| Exception Handling and Servicing Flowcharts |     |

## Floating-Point Unit

6

| Overview                                                       | 2   |

|----------------------------------------------------------------|-----|

| FPU Features                                                   |     |

| FPU Programming Model15                                        | 64  |

| Floating-Point General Registers (FGRs)15                      | 64  |

| Floating-Point Registers                                       | 6   |

| Floating-Point Control Registers15                             | 57  |

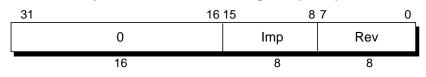

| Implementation and Revision Register, (FCR0)15                 |     |

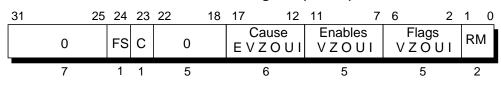

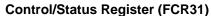

| Control/Status Register (FCR31)15                              | 9   |

| Accessing the Control/Status Register16                        |     |

| IEEE Standard 75416                                            | 51  |

| Control/Status Register FS Bit16                               | 51  |

| Control/Status Register Condition Bit16                        | 51  |

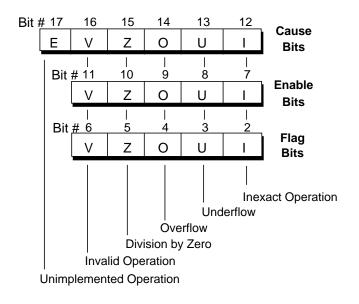

| Control/Status Register Cause, Flag, and Enable Fields         | 51  |

| Control/Status Register Rounding Mode Control Bits16           | 53  |

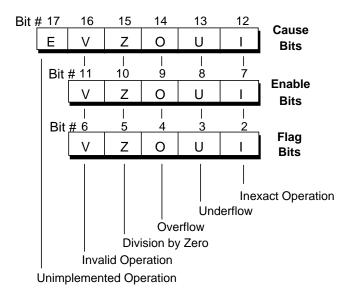

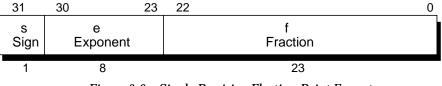

| Floating-Point Formats                                         | 54  |

| Binary Fixed-Point Format16                                    |     |

| Floating-Point Instruction Set Overview                        | 57  |

| Floating-Point Load, Store, and Move Instructions              |     |

| Transfers Between FPU and Memory16                             | ;9  |

| Transfers Between FPU and CPU16                                | ;9  |

| Load Delay and Hardware Interlocks16                           | ;9  |

| Data Alignment17                                               | '0  |

| Endianness17                                                   | '0  |

| Floating-Point Conversion Instructions17                       | '0  |

| Floating-Point Computational Instructions                      | '0  |

| Branch on FPU Condition Instructions17                         | '0  |

| Floating-Point Compare Operations17                            |     |

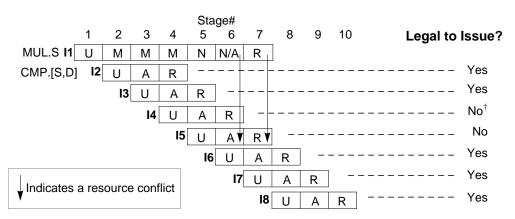

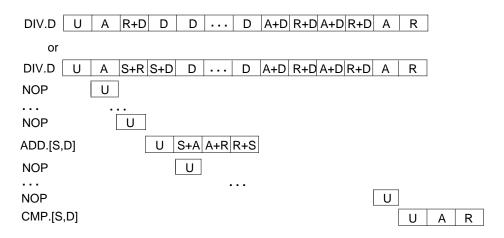

| FPU Instruction Pipeline Overview17                            | '2  |

| Instruction Execution17                                        | '2  |

| Instruction Execution Cycle Time17                             | '3  |

| Scheduling FPU Instructions17                                  | '5  |

| FPU Pipeline Overlapping17                                     | '5  |

| Instruction Scheduling Constraints17                           | '6  |

| Instruction Latency, Repeat Rate, and Pipeline Stage Sequences | 31  |

| Resource Scheduling Rules18                                    | \$2 |

|                                                                |     |

### 7

### Floating-Point Exceptions

| Exception Types                                |     |

|------------------------------------------------|-----|

| Exception Trap Processing                      |     |

| Flags                                          | 190 |

| FPU Exceptions                                 |     |

| Inexact Exception (I)                          | 192 |

| Invalid Operation Exception (V)                | 193 |

| Division-by-Zero Exception (Z)                 |     |

| Overflow Exception (O)                         |     |

| Underflow Exception (U)                        | 195 |

| Unimplemented Instruction Exception (E)        | 196 |

| Saving and Restoring State                     |     |

| Trap Handlers for IEEE Standard 754 Exceptions |     |

|                                                |     |

### 8

## **R4000 Processor Signal Descriptions**

| System Interface Signals          | 201 |

|-----------------------------------|-----|

| Clock/Control Interface Signals   | 203 |

| Secondary Cache Interface Signals | 205 |

| Interrupt Interface Signals       | 207 |

| JTAG Interface Signals            | 207 |

| Initialization Interface Signals  | 208 |

| Signal Summary                    | 209 |

|                                   |     |

### Initialization Interface

| Functional Overview      |  |

|--------------------------|--|

| Reset Signal Description |  |

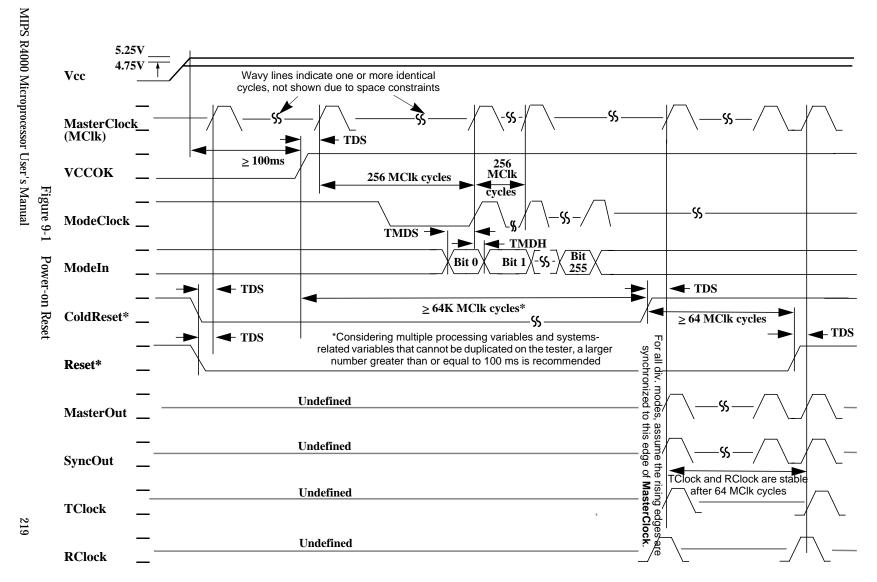

| Power-on Reset           |  |

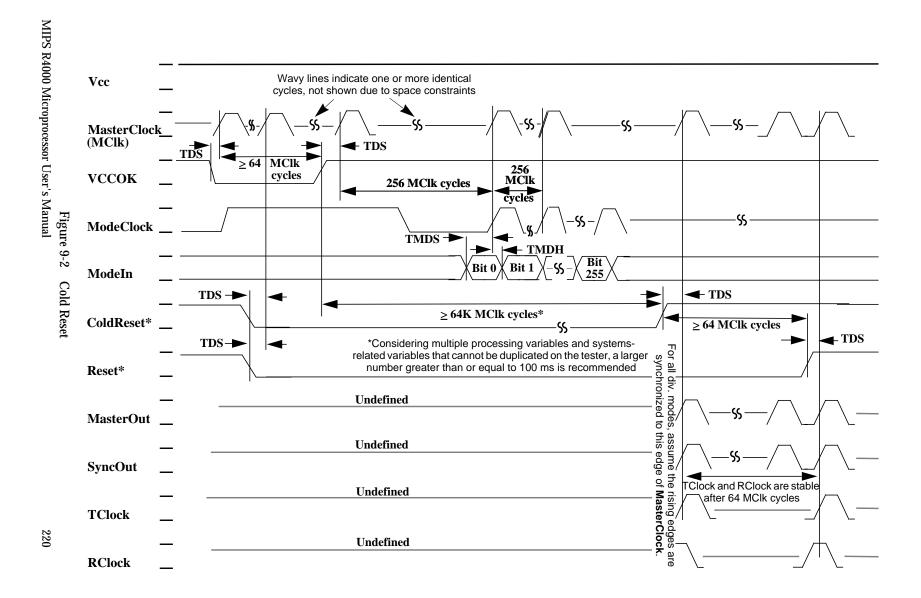

| Cold Reset               |  |

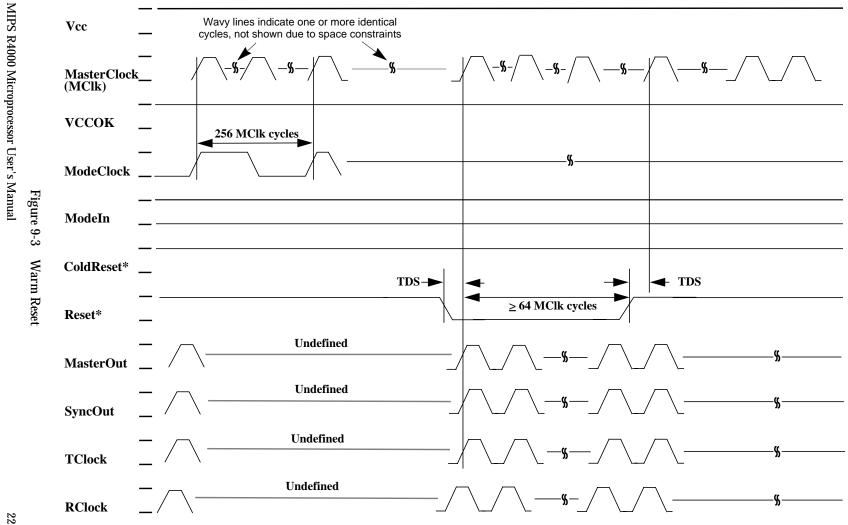

| Warm Reset               |  |

| Initialization Sequence  |  |

| Boot-Mode Settings       |  |

| -                        |  |

### 10

9

### **Clock Interface**

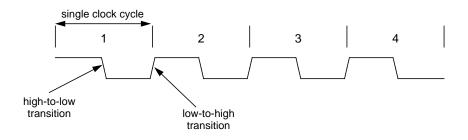

| Signal Terminology                                  | 228 |

|-----------------------------------------------------|-----|

| Basic System Clocks                                 | 229 |

| MasterClock                                         | 229 |

| MasterOut                                           | 229 |

| SyncIn/SyncOut                                      | 229 |

| PClock                                              | 229 |

| SClock                                              | 230 |

| TClock                                              | 230 |

| RClock                                              | 230 |

| PClock-to-SClock Division                           | 230 |

| System Timing Parameters                            | 233 |

| Alignment to SClock                                 | 233 |

| Alignment to MasterClock                            | 233 |

| Phase-Locked Loop (PLL)                             | 233 |

| Connecting Clocks to a Phase-Locked System          | 234 |

| Connecting Clocks to a System without Phase Locking | 235 |

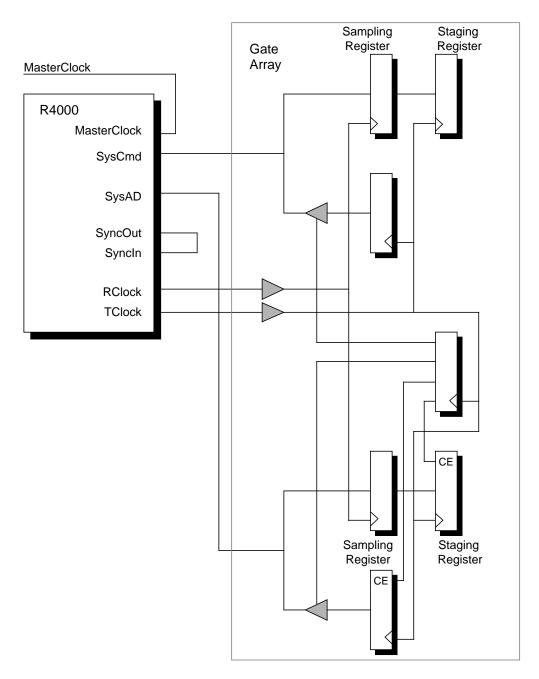

| Connecting to a Gate-Array Device                   | 235 |

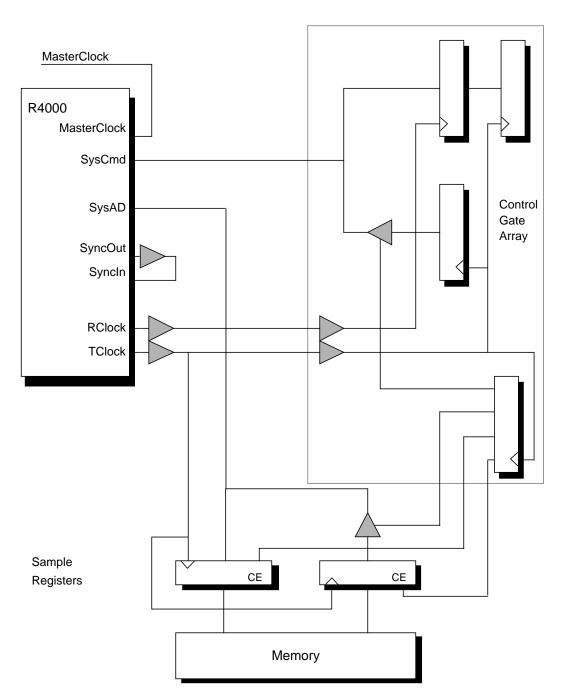

| Connecting to a CMOS Logic System                   | 238 |

| Processor Status Outputs                            | 241 |

#### 11

## Cache Organization, Operation, and Coherency

| Memory Organization                                     |

|---------------------------------------------------------|

| Overview of Cache Operations                            |

| R4000 Cache Description                                 |

| Secondary Cache Size                                    |

| Variable-Length Cache Lines                             |

| Cache Organization and Accessibility                    |

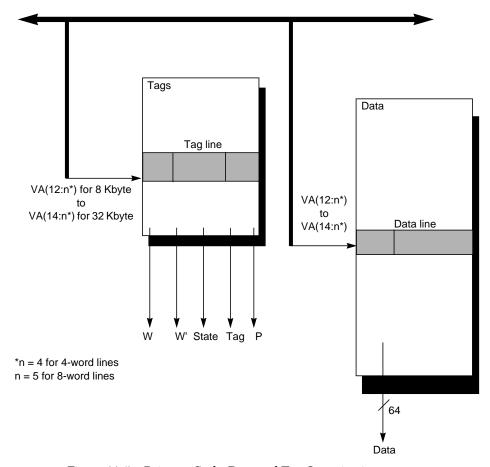

| Organization of the Primary Instruction Cache (I-Cache) |

| Organization of the Primary Data Cache (D-Cache)        |

| Accessing the Primary Caches                            |

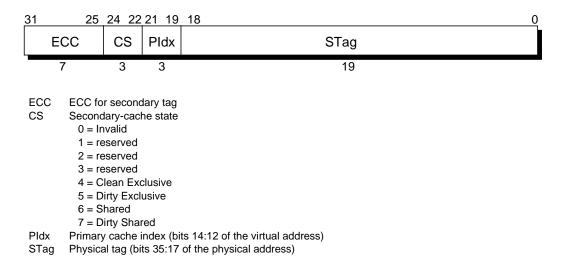

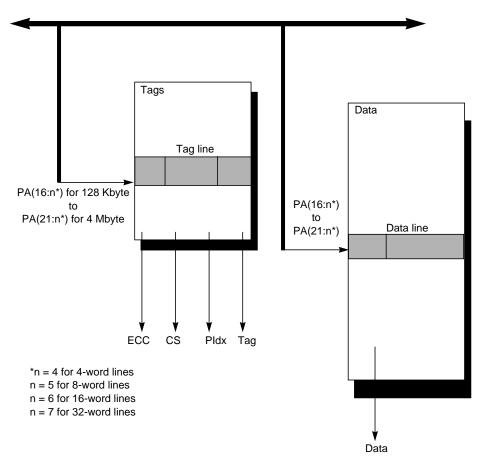

| Organization of the Secondary Cache                     |

| Accessing the Secondary Cache254                        |

| Cache States                                            |

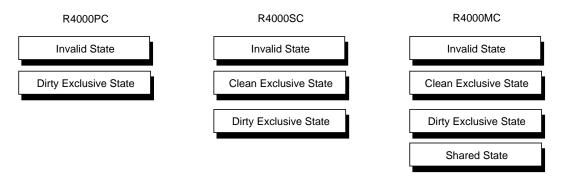

| Primary Cache States                                    |

| Secondary Cache States                                  |

| Mapping States Between Caches                           |

| Cache Line Ownership                                    |

| Cache Write Policy                                      |

| Cache State Transition Diagrams                         |

| Cache Coherency Overview                                |

| Cache Coherency Attributes                              |

| Uncached                                                |

| Noncoherent                                             |

| Sharable                                                |

| Update                                                  |

| Exclusive                                               |

| Cache Operation Modes                                   |

| Secondary-Cache Mode                                    |

| No-Secondary-Cache Mode                                 |

| Strong Ordering                                         |

| An Example of Strong Ordering                           |

| Testing for Strong Ordering                             |

| Restarting the Processor                                |

| Maintaining Coherency on Loads and Stores               |

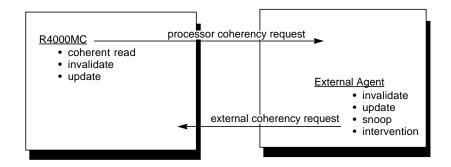

| Manipulation of the Cache by an External Agent          |

| Invalidate                                              |

| Update                                                  |

|                                                         |

MIPS R4000 Microprocessor User's Manual

| Snoop                                             |

|---------------------------------------------------|

| Intervention                                      |

| Coherency Conflicts                               |

| How Coherency Conflicts Arise                     |

| Processor Coherent Read Requests                  |

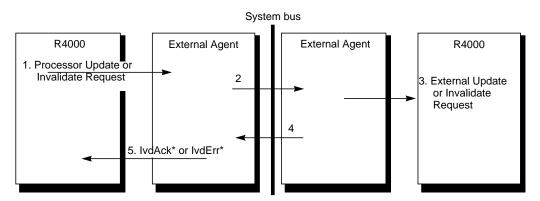

| Processor Invalidate or Update Requests           |

| External Coherency Requests                       |

| System Implications of Coherency Conflicts        |

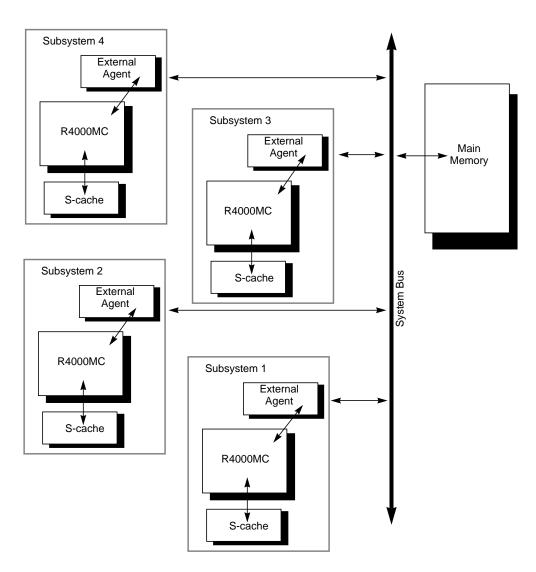

| System Model276                                   |

| Load                                              |

| Store                                             |

| Processor Coherent Read Request and Read Response |

| Processor Invalidate                              |

| Processor Write                                   |

| Handling Coherency Conflicts                      |

| Coherent Read Conflicts                           |

| Coherent Write Conflicts                          |

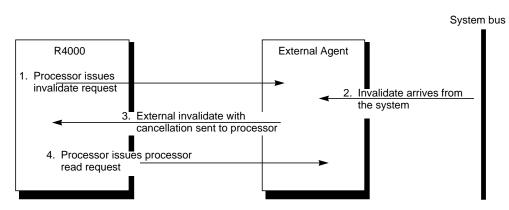

| Invalidate Conflicts                              |

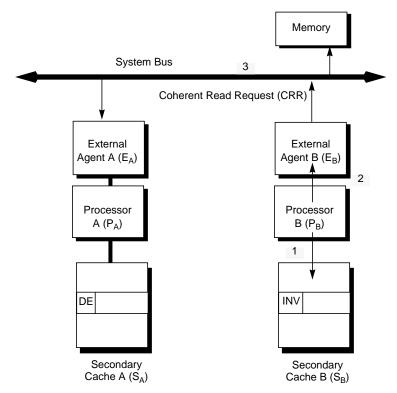

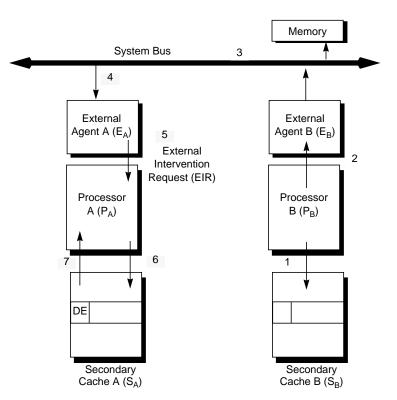

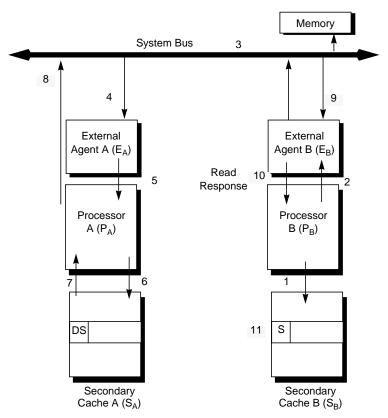

| Sample Cycle: Coherent Read Request               |

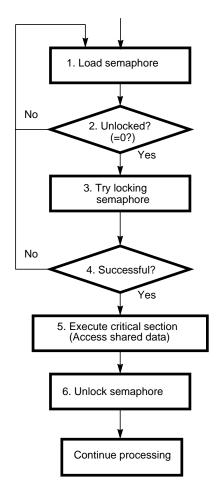

| R4000 Processor Synchronization Support           |

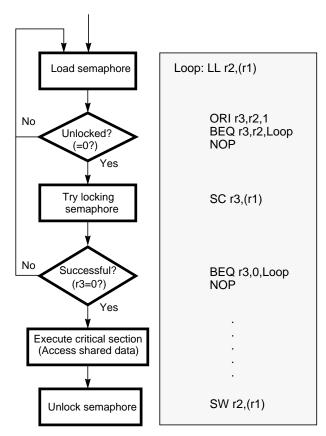

| Test-and-Set (Spinlock)                           |

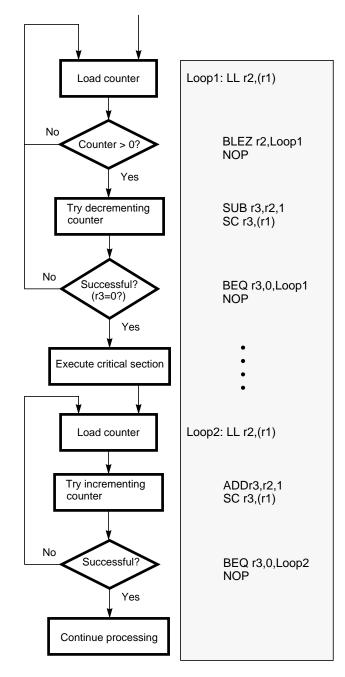

| Counter                                           |

| LL and SC                                         |

| Examples Using LL and SC                          |

### 12

## System Interface

| Terminology                         | :94        |

|-------------------------------------|------------|

| System Interface Description        |            |

| Interface Buses                     | :95        |

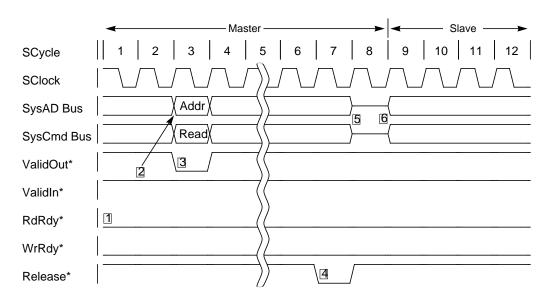

| Address and Data Cycles2            | 296        |

| Issue Cycles2                       | 296        |

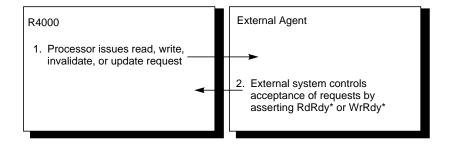

| Handshake Signals2                  | 298        |

| System Interface Protocols          |            |

| Master and Slave States2            | 299        |

| Moving from Master to Slave State 3 |            |

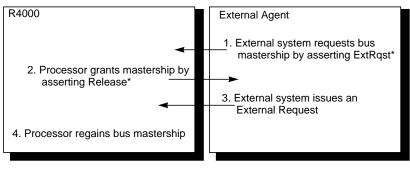

| External Arbitration                | 600        |

| Uncompelled Change to Slave State 3 | 601        |

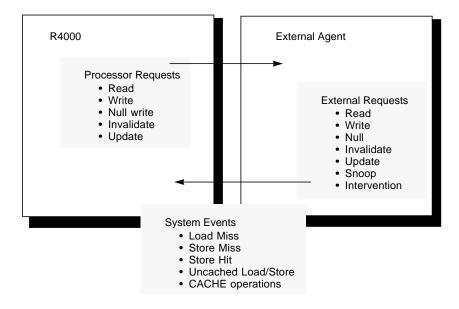

| Processor and External Requests     | 602        |

| Rules for Processor Requests        | 603        |

| Processor Requests                  | 604        |

| Processor Read Request              | 606        |

| Processor Write Request             | 607        |

| Processor Invalidate Request 3      | 808        |

| Processor Update Request3           | <b>510</b> |

| Clusters                            | 311        |

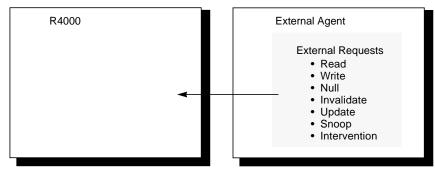

| External Requests                   | 513        |

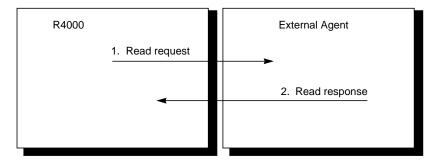

| External Read Request3              | 516        |

| External Write Request              | 616        |

| External Invalidate Request3        | 516        |

| External Update Request3            | 316        |

| External Snoop Request              |            |

| External Intervention Request       | 317        |

| Read Response                       | 317        |

| Handling Requests                   | 318        |

| Load Miss                           | 318        |

| Secondary-Cache Mode3               | 320        |

| No-Secondary-Cache Mode             | 320        |

| Store Miss                          | 521        |

| Secondary-Cache Mode3               |            |

| No-Secondary-Cache Mode3            |            |

| Store Hit3                          |            |

| Secondary-Cache Mode3               |            |

|                                     |            |

MIPS R4000 Microprocessor User's Manual

| No-Secondary-Cache Mode                          | 326 |

|--------------------------------------------------|-----|

| Uncached Loads or Stores                         | 326 |

| CACHE Operations                                 | 327 |

| Load Linked Store Conditional Operation          | 327 |

| Processor and External Request Protocols         | 329 |

| Processor Request Protocols                      | 330 |

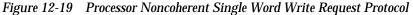

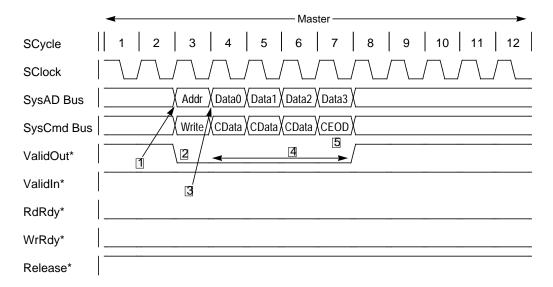

| Processor Read Request Protocol                  | 330 |

| Processor Write Request Protocol                 | 333 |

| Processor Invalidate and Update Request Protocol | 335 |

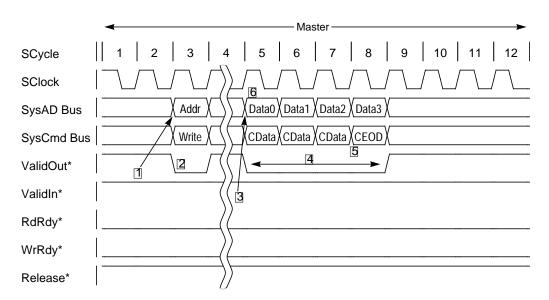

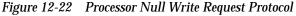

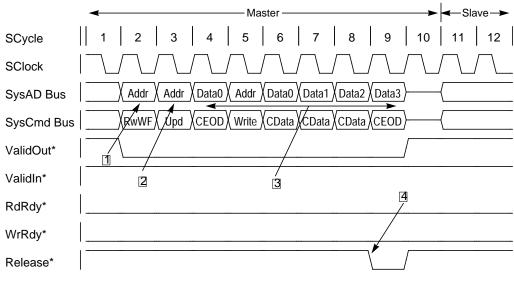

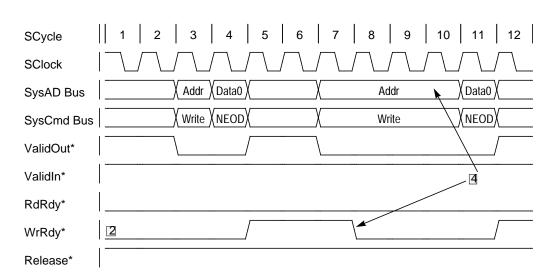

| Processor Null Write Request Protocol            | 336 |

| Processor Cluster Request Protocol               | 337 |

| Processor Request and Cluster Flow Control       | 338 |

| External Request Protocols                       | 341 |

| External Arbitration Protocol                    | 342 |

| External Read Request Protocol                   | 343 |

| External Null Request Protocol                   | 344 |

| External Write Request Protocol                  | 347 |

| External Invalidate and Update Request Protocols | 348 |

| External Intervention Request Protocol           | 349 |

| External Snoop Request Protocol                  | 352 |

| Read Response Protocol                           | 354 |

| Data Rate Control                                | 356 |

| Data Transfer Patterns                           | 356 |

| Secondary Cache Transfers                        | 357 |

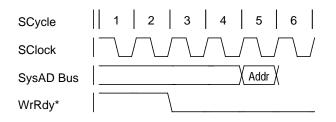

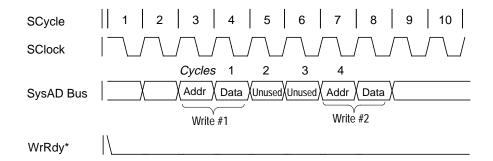

| Secondary Cache Write Cycle Time                 | 358 |

| Independent Transmissions on the SysAD Bus       | 359 |

| System Interface Endianness                      | 360 |

| System Interface Cycle Time                      | 361 |

| Cluster Request Spacing                          | 361 |

| Release Latency                                  | 362 |

| External Request Response Latency                | 363 |

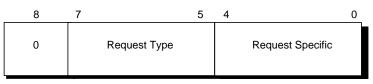

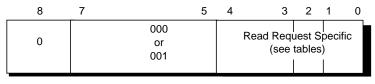

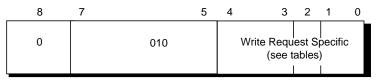

| System Interface Commands and Data Identifiers   | 364 |

| Command and Data Identifier Syntax               | 364 |

| System Interface Command Syntax                  | 365 |

| Read Requests                                    | 366 |

| Write Requests                                   | 367 |

| Null Requests                                    | 369 |

| Invalidate Requests                              | 370 |

|                                                  |     |

#### Table of Contents

| Update Requests                         |     |

|-----------------------------------------|-----|

| Intervention and Snoop Requests         |     |

| System Interface Data Identifier Syntax |     |

| Coherent Data                           |     |

| Noncoherent Data                        |     |

| Data Identifier Bit Definitions         | 375 |

| System Interface Addresses              |     |

| Addressing Conventions                  |     |

| Sequential and Subblock Ordering        |     |

| Processor Internal Address Map          |     |

### 13

## Secondary Cache Interface

| Data Transfer Rates                        |     |

|--------------------------------------------|-----|

| Duplicating Signals                        | 380 |

| Accessing a Split Secondary Cache          |     |

| SCDChk Bus                                 | 381 |

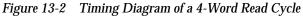

| SCTAG Bus                                  |     |

| Operation of the Secondary Cache Interface | 382 |

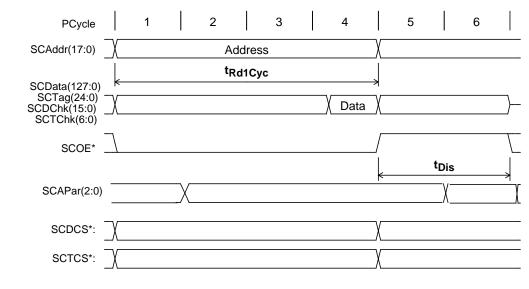

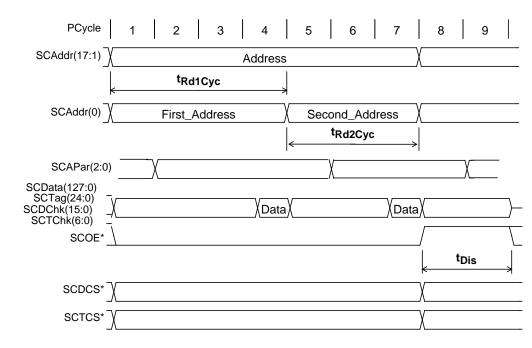

| Read Cycles                                | 383 |

| 4-Word Read Cycle                          | 383 |

| 8-Word Read Cycle                          |     |

| Notes on a Secondary Cache Read Cycle      | 384 |

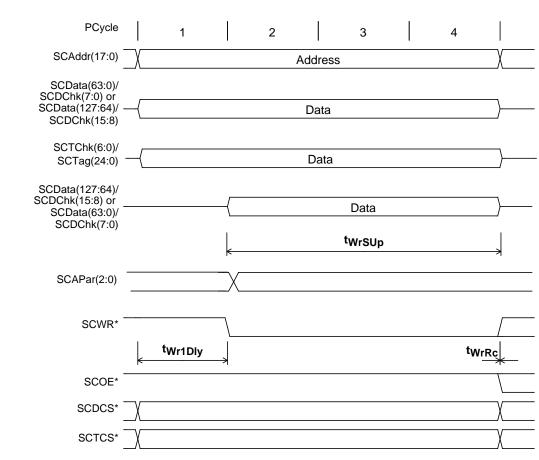

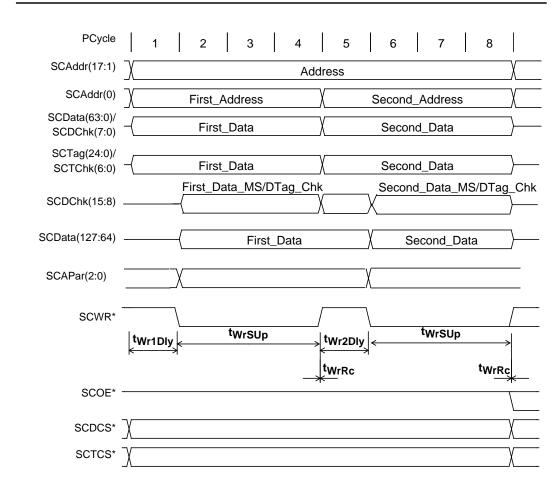

| Write Cycles                               | 385 |

| 4-Word Write Cycle                         | 385 |

| 8-Word Write Cycle                         |     |

| Notes on a Secondary Cache Write Cycle     |     |

|                                            |     |

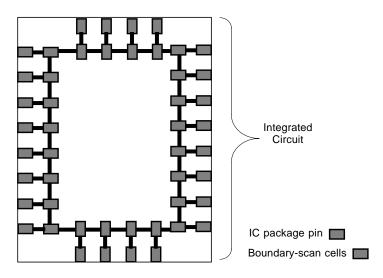

### 14 JTAG Interface

| What Boundary Scanning Is       | υ |

|---------------------------------|---|

| Signal Summary                  | 1 |

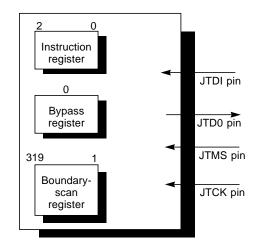

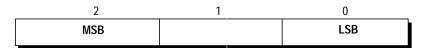

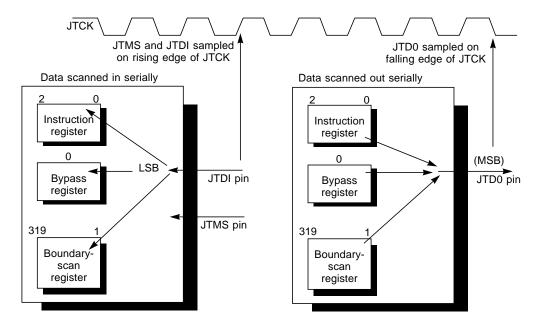

| JTAG Controller and Registers   | 2 |

| Instruction Register            | 2 |

| Bypass Register                 | 3 |

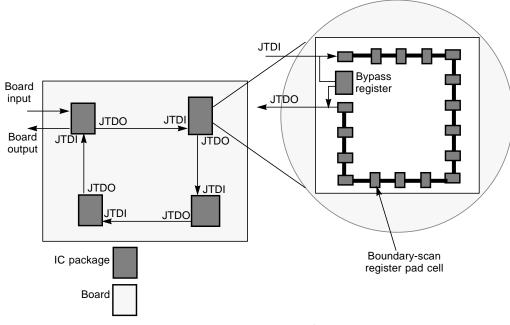

| Boundary-Scan Register          | 4 |

| Test Access Port (TAP)          | 5 |

| TAP Controller                  | 6 |

| Controller Reset                | 6 |

| Controller States               | 6 |

| Implementation-Specific Details | 0 |

### 15

## **R4000 Processor Interrupts**

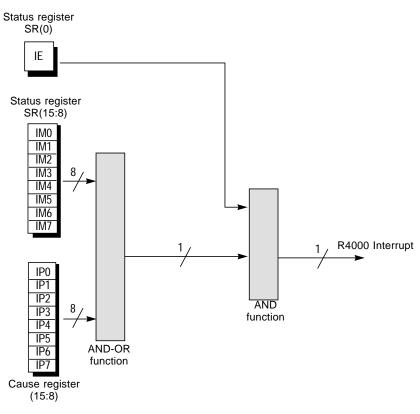

| Hardware Interrupts         | 402 |

|-----------------------------|-----|

| Nonmaskable Interrupt (NMI) |     |

| Asserting Interrupts        |     |

|                             |     |

### 16

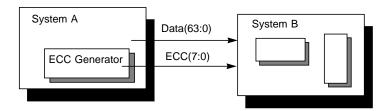

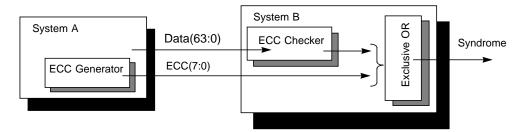

## Error Checking and Correcting

| Α | CPU Instruction Set Details                         |

|---|-----------------------------------------------------|

| B | FPU Instruction Set Details                         |

| С | Subblock Ordering                                   |

|   | Sequential OrderingC-2<br>Subblock OrderingC-2      |

| D | Output Buffer $\Delta i/\Delta t$ Control Mechanism |

|   | Mode BitsD-1                                        |

|   | Delay TimesD-2                                      |

| E | PLL Passive Components                              |

| F | Coprocessor 0 Hazards                               |

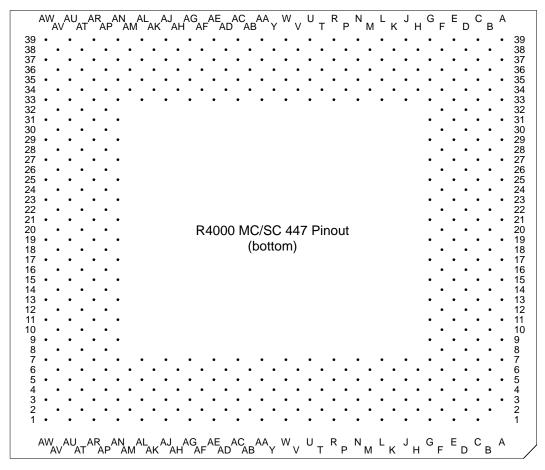

| G | R4000 Pinouts                                       |

|   | Pinout of R4000PCG-2                                |

|   | Pinout of R4000MC/SC Package PinoutG-5              |

### Index

Table of Contents

## Introduction

Historically, the evolution of computer architectures has been dominated by families of increasingly complex central processors. Under market pressures to preserve existing software, complex instruction set computer (CISC) architectures evolved by the accretion of microcode and increasingly intricate instruction sets. This intricacy in architecture was itself driven by the need to support high-level languages and operating systems, as advances in semiconductor technology made it possible to fabricate integrated circuits of greater and greater complexity. And at that time it seemed self-evident to designers that architectures should continue to become more and more complex as technological advances made such VLSI designs possible.

1

In recent years, however, reduced instruction set computer (RISC) architectures are implementing a different model for the interaction between hardware, firmware, and software. RISC concepts emerged from a statistical analysis of the way in which software actually uses processor resources: dynamic measurement of system kernels and object modules generated by optimizing compilers showed that the simplest instructions were used most often—even in the code for CISC machines. Correspondingly, complex instructions often went unused because their single way of performing a complex operation rarely matched the precise needs of a high-level language.

RISC architecture eliminates microcode routines and turns low-level control of the machine over to software. The RISC approach is not new, but its application has become more prevalent in recent years, due to the increasing use of high-level languages, the development of compilers that are able to optimize at the microcode level, and dramatic advances in semiconductor memory and packaging. It is now feasible to replace relatively slow microcode ROM with faster RAM that is organized as an instruction cache. Machine control resides in this instruction cache that is, in effect, customized on-the-fly: the instruction stream generated by system- and compiler-generated code provides a precise fit between the requirements of high-level software and the low-level capabilities of the hardware.

Reducing or simplifying the instruction set was not the primary goal of RISC architecture; it is a pleasant side effect of techniques used to gain the highest performance possible from available technology. Thus, the term *reduced instruction set computers* is a bit misleading; it is the push for performance that really drives and shapes RISC designs.

### 1.1 Benefits of RISC Design

Some benefits that result from RISC design techniques are not directly attributable to the drive to increase performance, but are a result of the basic reduction in complexity—a simpler design allows both chip-area resources and human resources to be applied to features that enhance performance. Some of these benefits are described below.

#### Shorter Design Cycle

The architectures of RISC processors can be implemented more quickly than their CISC counterparts: it is easier to fabricate and debug a streamlined, simplified architecture with no microcode than a complex architecture that uses microcode. CISC processors have such a long design cycle that they may not be completely debugged by the time they are technologically obsolete. The shorter time required to design and implement RISC processors allows them to make use of the best available technologies.

#### **Effective Utilization of Chip Area**

The simplicity of RISC processors also frees scarce chip geography for performance-critical resources such as larger register files, translation lookaside buffers (TLBs), coprocessors, and fast multiply and divide units. Such resources help RISC processors obtain an even greater performance edge.

#### **User (Programmer) Benefits**

Simplicity in architecture also helps the user by providing a uniform instruction set that is easier to use. This allows a closer correlation between the instruction count and the cycle count, making it easier to measure code optimization activities.

#### **Advanced Semiconductor Technologies**

Each new VLSI technology is introduced with tight limits on the number of transistors that fit on each chip. Since the simplicity of a RISC processor allows it to be implemented in fewer transistors than its CISC counterpart, the first computers capable of exploiting these new VLSI technologies have been using and will continue to use RISC architecture.

#### **Optimizing Compilers**

RISC architecture is designed so that the compilers, not assembly languages, have the optimal working environment. RISC philosophy assumes that high-level language programming is used, which contradicts the older CISC philosophy that assumes assembly language programming is of primary importance.

The trend toward high-level language instructions has led to the development of more efficient compilers to convert high-level language instructions to machine code. Primary measures of compiler efficiency are the compactness of its generated code and the shortness of its execution time.

During the development of more efficient compilers, analysis of instruction streams revealed that the greatest amount of time was spent executing simple instructions and performing load and store operations, while the more complex instructions were used less frequently. It was also learned that compilers produce code that is often a narrow subset of the processor instruction set architecture (ISA). A compiler works more efficiently with instructions that perform simple, well-defined operations and generate minimal side-effects. Compilers do not use complex instructions and features; the more complex, powerful instructions are either too difficult for the compiler to employ or those instructions do not precisely fit high-level language requirements.

Thus, a natural match exists between RISC architectures and efficient, optimizing compilers. This match makes it easier for compilers to generate the most effective sequences of machine instructions to accomplish tasks defined by the high-level language.

#### **MIPS RISCompiler Language Suite**

Some compiler products are derived from disparate sources and consequently do not fit together very well. Instead of treating each language's compiler as a separate entity, the MIPS RISCompiler<sup>TM</sup> language suite shares common elements across the entire family of compilers. In this way the language suite offers both tight integration and broad language coverage.

The MIPS language suite supports:

- industry-standard front ends for the following languages (C, FORTRAN, Pascal)

- a common intermediate language, offering an efficient way to add language front ends over time

- all of the back end optimization and code generation

- the same object format and calling conventions

- mixed-language programs

- debugging of programs written in all languages, including mixtures

This language suite approach yields high-quality compilers for all languages, since common elements make up the majority of each of the language products. In addition, this approach provides the ability to develop and execute multi-language programs, promoting flexibility in development, avoiding the necessity of recoding proven program segments, and protecting the user's software investment. The common back-end also exports optimizing and code-generating improvements immediately throughout the language suite, thereby reducing maintenance.

#### **1.2 Compatibility**

The R4000 processor provides complete application software compatibility with the MIPS R2000, R3000, and R6000 processors. Although the MIPS processor architecture has evolved in response to a compromise between software and hardware resources in the computer system, the R4000 processor implements the MIPS ISA for user-mode programs. This guarantees that user programs conforming to the ISA execute on any MIPS hardware implementation.

#### **1.3 Processor General Features**

This section briefly describes the programming model, the memory management unit (MMU), and the caches in the R4000 processor. A more detailed description is given in succeeding sections.

- Full 32-bit and 64-bit Operations. The R4000 processor contains 32 general purpose 64-bit registers. (When operating as a 32-bit processor, the general purpose registers are 32-bits wide.) All instructions are 32 bits wide.

- Efficient Pipeline. The superpipeline design of the processor results in an execution rate approaching one instruction per cycle. Pipeline stalls and exceptional events are handled precisely and efficiently.

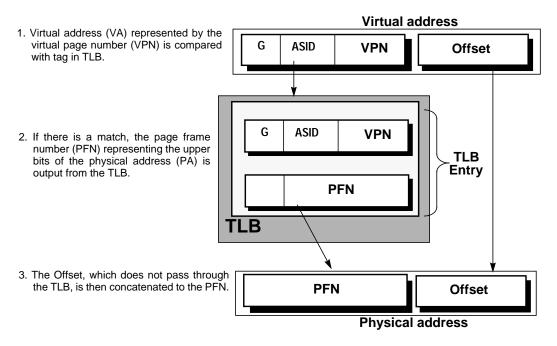

- **MMU**. The R4000 processor uses an on-chip TLB that provides rapid virtual-to-physical address translation.

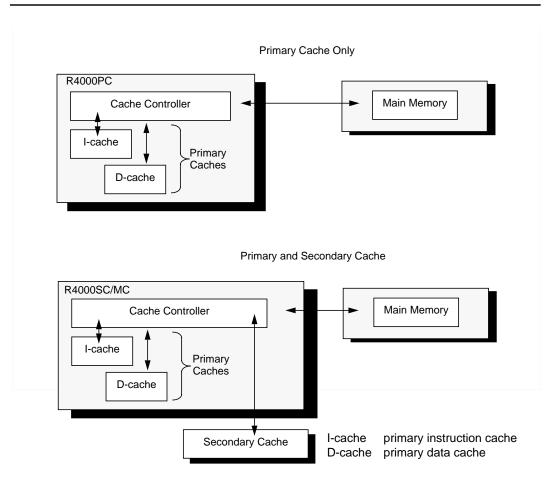

- **Cache Control.** The R4000 primary instruction and data caches reside on-chip, and can each hold 8 Kbytes. In the R4400 processor, the primary caches can each hold 16 Kbytes. Architecturally, each primary cache can be increased to hold up to 32 Kbytes. An off-chip secondary cache (R4000SC and R4000MC processors only) can hold from 128 Kbytes to 4 Mbytes. All processor cache control logic, including the secondary cache control logic, is on-chip.

- **Floating-Point Unit**. The FPU is located on-chip and implements the ANSI/IEEE standard 754-1985.

# 1.4 R4000 Processor Configurations

The R4000 processor<sup>†</sup> is packaged in three different configurations. All processors are implemented in sub-1-micron CMOS technology.

- **R4000PC** is designed for cost-sensitive systems such as inexpensive desktop systems and high-end embedded controllers. It is packaged in a 179-pin PGA, and does not support a secondary cache.

- **R4000SC** is designed for high-performance uniprocessor systems. It is packaged in a 447-pin LGA/PGA and includes integrated control for large secondary caches built from standard SRAMs.

- **R4000MC** is designed for large cache-coherent multiprocessor systems. It is packaged in a 447-pin LGA/PGA and, in addition to the features of R4000SC, includes support for a wide variety of bus designs and cache-coherency mechanisms.

Table 1-1 lists the features in each of the three configurations (**X** indicates the feature is present). R4400 processor enhancements are described in the section following.

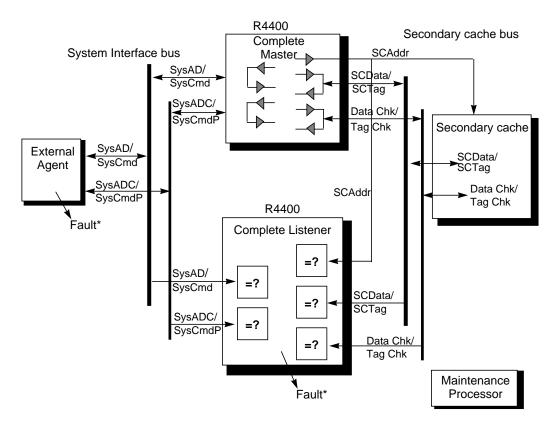

# 1.5 R4400 Processor Enhancements

In addition to the features contained in the R4000 processor, the R4400 processor has the following enhancements:

- fully functional Status pins (described in Chapter 10)

- Master/Checker mode (described in Chapter 16)

- larger primary caches (described in Processor General Features, in this chapter)

- uncached store buffer (described in Chapter 3)

- divide-by-6 and divide-by-8 modes (described in Chapter 10)

- cache error bit, *EW*, added to the *CacheErr* register (described in Chapter 5).

<sup>&</sup>lt;sup>†</sup> Features of the R4400 processor that differ from the R4000 processor are noted throughout this book; for instance, R4400 processor enhancements are listed in the next section. Otherwise, references to the R4000 processor may be taken to include the R4400 processor.

# Chapter 1

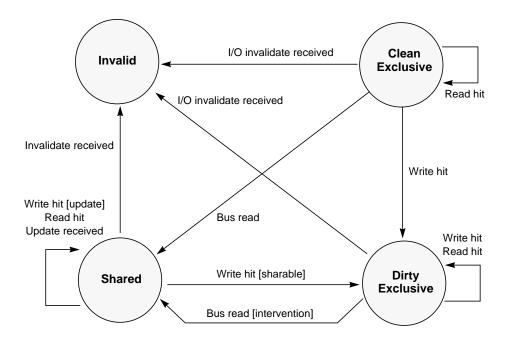

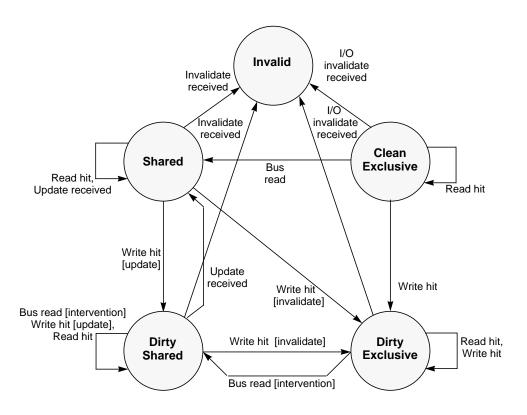

| Feature                   | R4000PC             | R4000SC | R4000MC |

|---------------------------|---------------------|---------|---------|

| Primary Cache States      |                     |         |         |

| Valid                     | X                   | X       | X       |

| Shared                    |                     |         | X       |

| Clean Exclusive           |                     | X       | X       |

| Dirty Exclusive           | X                   | X       | X       |

| Secondary Cache Interface |                     | X       | X       |

| Sec                       | condary Cache State | es —    |         |

| Valid                     | X                   | X       | X       |

| Shared                    |                     |         | X       |

| Dirty Shared              |                     |         | X       |

| Clean Exclusive           |                     | X       | X       |

| Dirty Exclusive           | X                   | X       | X       |

| Multiprocessing           |                     |         | X       |

| Cache                     | e Coherency Attrib  | utes    |         |

| Uncached                  | X                   | X       | X       |

| Noncoherent               | X                   | X       | X       |

| Sharable                  |                     |         | X       |

| Update                    |                     |         | X       |

| Exclusive                 |                     |         | X       |

|                           | Packages            |         |         |

| PGA (179-pin)             | X                   |         |         |

| PGA (447-pin)             |                     | X       | X       |

Table 1-1 R4000 Features

# 1.6 R4000 Processor

This section describes the following:

- the 64-bit architecture of the R4000 processor

- the superpipeline design of the CPU instruction pipeline (described in detail in Chapter 3)

- an overview of the System interface (described in detail in Chapter 12)

- an overview of the CPU registers (detailed in Chapters 4 and 5) and CPU instruction set (detailed in Chapter 2 and Appendix A)

- data formats and byte ordering

- the System Control Coprocessor, CP0, and the floating-point unit, CP1

- caches and memory, including a description of primary and secondary caches, the memory management unit (MMU), the translation lookaside buffer (TLB), and the Secondary Cache interface (described in more detail in Chapters 4 and 11). The Secondary Cache interface is detailed in Chapter 13.

# **64-bit Architecture**

The natural mode of operation for the R4000 processor is as a 64-bit microprocessor; however, 32-bit applications maintain compatibility even when the processor operates as a 64-bit processor.

The R4000 processor provides the following:

- 64-bit on-chip floating-point unit (FPU)

- 64-bit integer arithmetic logic unit (ALU)

- 64-bit integer registers

- 64-bit virtual address space

- 64-bit system bus

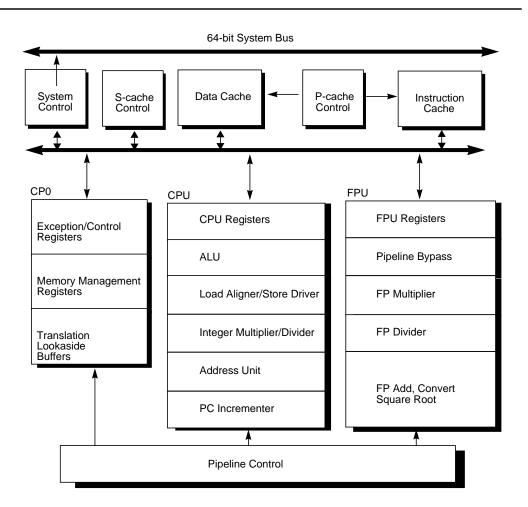

Figure 1-1 is a block diagram of the R4000 processor internals.

Figure 1-1 R4000 Processor Internal Block Diagram

# **Superpipeline Architecture**

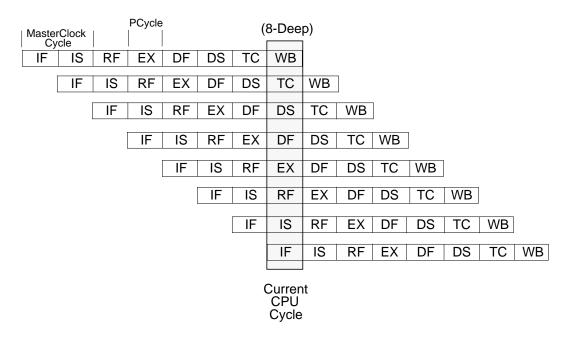

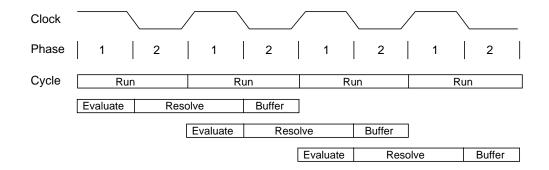

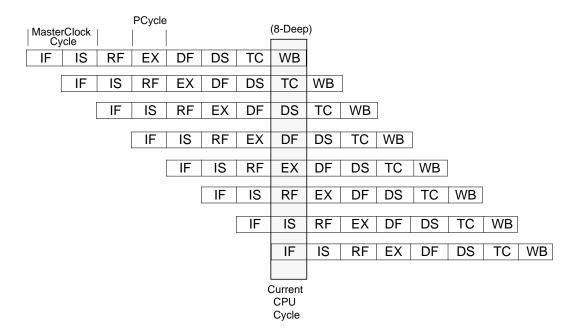

The R4000 processor exploits instruction parallelism by using an eightstage superpipeline which places no restrictions on the instruction issued. Under normal circumstances, two instructions are issued each cycle.

The internal pipeline of the R4000 processor operates at twice the frequency of the master clock, as discussed in Chapter 3. The processor achieves high throughput by pipelining cache accesses, shortening register access times, implementing virtual-indexed primary caches, and allowing the latency of functional units to span more than one pipeline clock cycles.

# **System Interface**

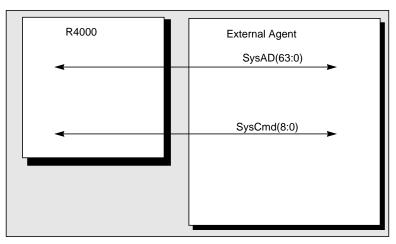

The R4000 processor supports a 64-bit System interface that can construct uniprocessor systems with a direct DRAM interface—with or without a secondary cache—or cache-coherent multiprocessor systems. The System interface includes:

- a 64-bit multiplexed address and data bus

- 8 check bits

- a 9-bit parity-protected command bus

- 8 handshake signals

The interface is capable of transferring data between the processor and memory at a peak rate of 400 Mbytes/second, when running at 50 MHz.

# **CPU Register Overview**

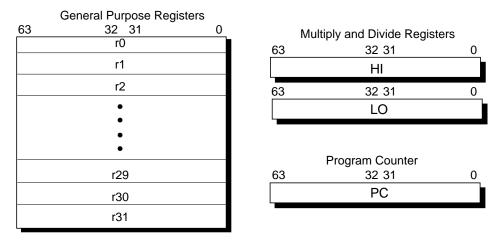

The central processing unit (CPU) provides the following registers:

- 32 general purpose registers

- a Program Counter (PC) register

- 2 registers that hold the results of integer multiply and divide operations (*HI* and *LO*).

Floating-point unit (FPU) registers are described in Chapter 6.

CPU registers can be either 32 bits or 64 bits wide, depending on the R4000 processor mode of operation.

Figure 1-2 shows the CPU registers.

Register width depends on mode of operation: 32-bit or 64-bit

Figure 1-2 CPU Registers

Two of the CPU general purpose registers have assigned functions:

- *r0* is hardwired to a value of zero, and can be used as the target register for any instruction whose result is to be discarded. *r0* can also be used as a source when a zero value is needed.

- *r31* is the link register used by Jump and Link instructions. It should not be used by other instructions.

The CPU has three special purpose registers:

- *PC* Program Counter register

- *HI* Multiply and Divide register higher result

- *LO* Multiply and Divide register lower result

The two Multiply and Divide registers (HI, LO) store:

- the product of integer multiply operations, or

- the quotient (in *LO*) and remainder (in *HI*) of integer divide operations

The R4000 processor has no *Program Status Word* (PSW) register as such; this is covered by the *Status* and *Cause* registers incorporated within the System Control Coprocessor (CP0). CP0 registers are described later in this chapter.

# **CPU Instruction Set Overview**

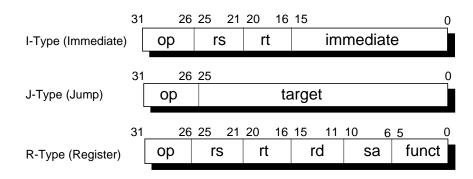

Each CPU instruction is 32 bits long. As shown in Figure 1-3, there are three instruction formats:

- immediate (I-type)

- jump (J-type)

- register (R-type)

#### Figure 1-3 CPU Instruction Formats

Each format contains a number of different instructions, which are described further in this chapter. Fields of the instruction formats are described in Chapter 2.

Instruction decoding is greatly simplified by limiting the number of formats to these three. This limitation means that the more complicated (and less frequently used) operations and addressing modes can be synthesized by the compiler, using sequences of these same simple instructions. The instruction set can be further divided into the following groupings:

- **Load and Store** instructions move data between memory and general registers. They are all immediate (I-type) instructions, since the only addressing mode supported is base register plus 16-bit, signed immediate offset.

- **Computational** instructions perform arithmetic, logical, shift, multiply, and divide operations on values in registers. They include register (R-type, in which both the operands and the result are stored in registers) and immediate (I-type, in which one operand is a 16-bit immediate value) formats.

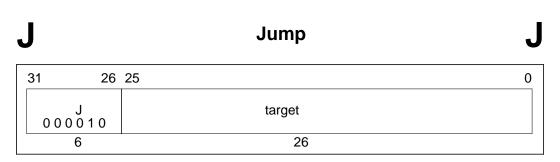

- Jump and Branch instructions change the control flow of a program. Jumps are always made to a paged, absolute address formed by combining a 26-bit target address with the high-order bits of the Program Counter (J-type format) or register address (R-type format). Branches have 16-bit offsets relative to the program counter (I-type). Jump And Link instructions save their return address in register 31.

- **Coprocessor** instructions perform operations in the coprocessors. Coprocessor load and store instructions are I-type.

- **Coprocessor 0** (system coprocessor) instructions perform operations on CP0 registers to control the memory management and exception handling facilities of the processor. These are listed in Table 1-18.

- **Special** instructions perform system calls and breakpoint operations. These instructions are always R-type.

- **Exception** instructions cause a branch to the general exceptionhandling vector based upon the result of a comparison. These instructions occur in both R-type (both the operands and the result are registers) and I-type (one operand is a 16-bit immediate value) formats.

Chapter 2 provides a more detailed summary and Appendix A gives a complete description of each instruction.

Tables 1-2 through 1-17 list CPU instructions common to MIPS R-Series processors, along with those instructions that are extensions to the instruction set architecture. The extensions result in code space reductions, multiprocessor support, and improved performance in operating system kernel code sequences—for instance, in situations where run-time bounds-checking is frequently performed. Table 1-18 lists CP0 instructions.

| OpCode | Description            |

|--------|------------------------|

| LB     | Load Byte              |

| LBU    | Load Byte Unsigned     |

| LH     | Load Halfword          |

| LHU    | Load Halfword Unsigned |

| LW     | Load Word              |

| LWL    | Load Word Left         |

| LWR    | Load Word Right        |

| SB     | Store Byte             |

| SH     | Store Halfword         |

| SW     | Store Word             |

| SWL    | Store Word Left        |

| SWR    | Store Word Right       |

Table 1-2

CPU Instruction Set: Load and Store Instructions

Table 1-3

CPU Instruction Set: Arithmetic Instructions (ALU Immediate)

| OpCode | Description                         |

|--------|-------------------------------------|

| ADDI   | Add Immediate                       |

| ADDIU  | Add Immediate Unsigned              |

| SLTI   | Set on Less Than Immediate          |

| SLTIU  | Set on Less Than Immediate Unsigned |

| ANDI   | AND Immediate                       |

| ORI    | OR Immediate                        |

| XORI   | Exclusive OR Immediate              |

| LUI    | Load Upper Immediate                |

| OpCode | Description               |

|--------|---------------------------|

| ADD    | Add                       |

| ADDU   | Add Unsigned              |

| SUB    | Subtract                  |

| SUBU   | Subtract Unsigned         |

| SLT    | Set on Less Than          |

| SLTU   | Set on Less Than Unsigned |

| AND    | AND                       |

| OR     | OR                        |

| XOR    | Exclusive OR              |

| NOR    | NOR                       |

Table 1-4

CPU Instruction Set: Arithmetic (3-Operand, R-Type)

Table 1-5

CPU Instruction Set: Multiply and Divide Instructions

| OpCode | Description       |

|--------|-------------------|

| MULT   | Multiply          |

| MULTU  | Multiply Unsigned |

| DIV    | Divide            |

| DIVU   | Divide Unsigned   |

| MFHI   | Move From HI      |

| MTHI   | Move To HI        |

| MFLO   | Move From LO      |

| MTLO   | Move To LO        |

| OpCode | Description                                      |

|--------|--------------------------------------------------|

| J      | Jump                                             |

| JAL    | Jump And Link                                    |

| JR     | Jump Register                                    |

| JALR   | Jump And Link Register                           |

| BEQ    | Branch on Equal                                  |

| BNE    | Branch on Not Equal                              |

| BLEZ   | Branch on Less Than or Equal to Zero             |

| BGTZ   | Branch on Greater Than Zero                      |

| BLTZ   | Branch on Less Than Zero                         |

| BGEZ   | Branch on Greater Than or Equal to Zero          |

| BLTZAL | Branch on Less Than Zero And Link                |

| BGEZAL | Branch on Greater Than or Equal to Zero And Link |

Table 1-6

CPU Instruction Set: Jump and Branch Instructions

Table 1-7

CPU Instruction Set: Shift Instructions

| OpCode | Description                     |

|--------|---------------------------------|

| SLL    | Shift Left Logical              |

| SRL    | Shift Right Logical             |

| SRA    | Shift Right Arithmetic          |

| SLLV   | Shift Left Logical Variable     |

| SRLV   | Shift Right Logical Variable    |

| SRAV   | Shift Right Arithmetic Variable |

| OpCode | Description                     |

|--------|---------------------------------|

| LWCz   | Load Word to Coprocessor z      |

| SWCz   | Store Word from Coprocessor z   |

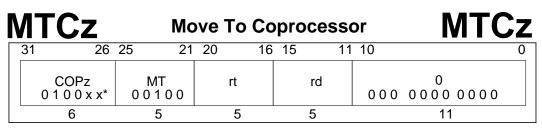

| MTCz   | Move To Coprocessor z           |

| MFCz   | Move From Coprocessor z         |

| CTCz   | Move Control to Coprocessor z   |

| CFCz   | Move Control From Coprocessor z |

| COPz   | Coprocessor Operation z         |

| BCzT   | Branch on Coprocessor z True    |

| BCzF   | Branch on Coprocessor z False   |

Table 1-8

CPU Instruction Set: Coprocessor Instructions

Table 1-9

CPU Instruction Set: Special Instructions

| OpCode  | Description |

|---------|-------------|

| SYSCALL | System Call |

| BREAK   | Break       |

| OpCode | Description                  |

|--------|------------------------------|

| LD     | Load Doubleword              |

| LDL    | Load Doubleword Left         |

| LDR    | Load Doubleword Right        |

| LL     | Load Linked                  |

| LLD    | Load Linked Doubleword       |

| LWU    | Load Word Unsigned           |

| SC     | Store Conditional            |

| SCD    | Store Conditional Doubleword |

| SD     | Store Doubleword             |

| SDL    | Store Doubleword Left        |

| SDR    | Store Doubleword Right       |

| SYNC   | Sync                         |

Table 1-10

Extensions to the ISA: Load and Store Instructions

Table 1-11

Extensions to the ISA: Arithmetic Instructions (ALU Immediate)

| OpCode | Description                       |

|--------|-----------------------------------|

| DADDI  | Doubleword Add Immediate          |

| DADDIU | Doubleword Add Immediate Unsigned |

Table 1-12

Extensions to the ISA: Multiply and Divide Instructions

| OpCode | Description                  |

|--------|------------------------------|

| DMULT  | Doubleword Multiply          |

| DMULTU | Doubleword Multiply Unsigned |

| DDIV   | Doubleword Divide            |

| DDIVU  | Doubleword Divide Unsigned   |

| OpCode  | Description                                                |  |  |  |  |

|---------|------------------------------------------------------------|--|--|--|--|

| BEQL    | Branch on Equal Likely                                     |  |  |  |  |

| BNEL    | Branch on Not Equal Likely                                 |  |  |  |  |

| BLEZL   | Branch on Less Than or Equal to Zero Likely                |  |  |  |  |

| BGTZL   | Branch on Greater Than Zero Likely                         |  |  |  |  |

| BLTZL   | Branch on Less Than Zero Likely                            |  |  |  |  |

| BGEZL   | Branch on Greater Than or Equal to Zero Likely             |  |  |  |  |

| BLTZALL | Branch on Less Than Zero And Link Likely                   |  |  |  |  |

| BGEZALL | Branch on Greater Than or Equal to Zero And Link<br>Likely |  |  |  |  |

| BCzTL   | Branch on Coprocessor z True Likely                        |  |  |  |  |

| BCzFL   | Branch on Coprocessor z False Likely                       |  |  |  |  |

Table 1-13

Extensions to the ISA: Branch Instructions

Table 1-14

Extensions to the ISA: Arithmetic Instructions (3-operand, R-type)

| OpCode | Description                  |  |  |

|--------|------------------------------|--|--|

| DADD   | Doubleword Add               |  |  |

| DADDU  | Doubleword Add Unsigned      |  |  |

| DSUB   | Doubleword Subtract          |  |  |

| DSUBU  | Doubleword Subtract Unsigned |  |  |

| OpCode | Description                                |

|--------|--------------------------------------------|

| DSLL   | Doubleword Shift Left Logical              |

| DSRL   | Doubleword Shift Right Logical             |

| DSRA   | Doubleword Shift Right Arithmetic          |

| DSLLV  | Doubleword Shift Left Logical Variable     |

| DSRLV  | Doubleword Shift Right Logical Variable    |

| DSRAV  | Doubleword Shift Right Arithmetic Variable |

| DSLL32 | Doubleword Shift Left Logical + 32         |

| DSRL32 | Doubleword Shift Right Logical + 32        |

| DSRA32 | Doubleword Shift Right Arithmetic + 32     |

Table 1-15

Extensions to the ISA: Shift Instructions

| Table 1-16  | Extensions to the ISA: Exception Instructions |

|-------------|-----------------------------------------------|

| 1 4010 1 10 |                                               |

| OpCode | Description                                         |  |  |

|--------|-----------------------------------------------------|--|--|

| TGE    | Trap if Greater Than or Equal                       |  |  |

| TGEU   | Trap if Greater Than or Equal Unsigned              |  |  |

| TLT    | Trap if Less Than                                   |  |  |

| TLTU   | Trap if Less Than Unsigned                          |  |  |

| TEQ    | Trap if Equal                                       |  |  |

| TNE    | Trap if Not Equal                                   |  |  |

| TGEI   | Trap if Greater Than or Equal Immediate             |  |  |

| TGEIU  | Trap if Greater Than or Equal Immediate<br>Unsigned |  |  |

| TLTI   | Trap if Less Than Immediate                         |  |  |

| TLTIU  | Trap if Less Than Immediate Unsigned                |  |  |

| TEQI   | Trap if Equal Immediate                             |  |  |

| TNEI   | Trap if Not Equal Immediate                         |  |  |

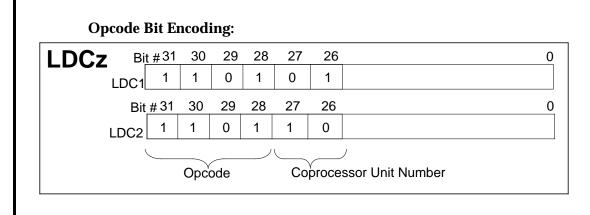

| Table 1-17 | Extensions to the ISA: Coprocessor Instructions |  |

|------------|-------------------------------------------------|--|

|------------|-------------------------------------------------|--|

| OpCode | Description                        |

|--------|------------------------------------|

| DMFCz  | Doubleword Move From Coprocessor z |

| DMTCz  | Doubleword Move To Coprocessor z   |

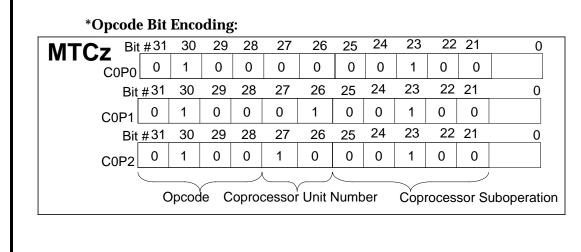

| LDCz   | Load Double Coprocessor z          |

| SDCz   | Store Double Coprocessor z         |

#### Table 1-18 CP0 Instructions

| OpCode | Description                  |

|--------|------------------------------|

| DMFC0  | Doubleword Move From CP0     |

| DMTC0  | Doubleword Move To CP0       |

| MTC0   | Move to CP0                  |

| MFC0   | Move from CP0                |

| TLBR   | Read Indexed TLB Entry       |

| TLBWI  | Write Indexed TLB Entry      |

| TLBWR  | Write Random TLB Entry       |

| TLBP   | Probe TLB for Matching Entry |

| CACHE  | Cache Operation              |

| ERET   | Exception Return             |

## **Data Formats and Addressing**

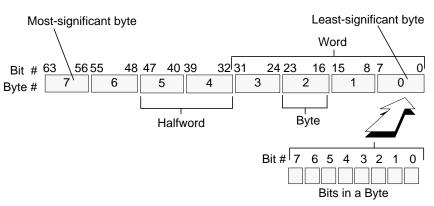

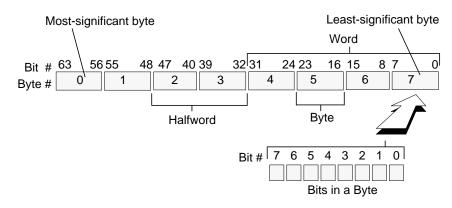

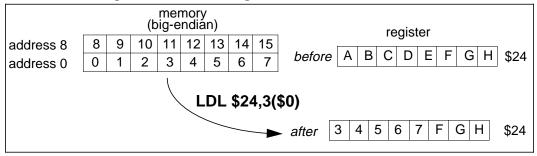

The R4000 processor uses four data formats: a 64-bit doubleword, a 32-bit word, a 16-bit halfword, and an 8-bit byte. Byte ordering within each of the larger data formats—halfword, word, doubleword—can be configured in either big-endian or little-endian order. Endianness refers to the location of byte 0 within the multi-byte data structure. Figures 1-4 and 1-5 show the ordering of bytes within words and the ordering of words within multiple-word structures for the big-endian and little-endian conventions.

When the R4000 processor is configured as a big-endian system, byte 0 is the most-significant (leftmost) byte, thereby providing compatibility with MC  $68000^{\degree}$  and IBM  $370^{\degree}$  conventions. Figure 1-4 shows this configuration.

| Higher           | Word    | Bit <sub>1</sub> # |       |       |     |  |

|------------------|---------|--------------------|-------|-------|-----|--|

| Address          | Address | 31 24              | 23 16 | 615 8 | 7 0 |  |

| $\bigwedge$      | 12      | 12                 | 13    | 14    | 15  |  |

| 1                | 8       | 8                  | 9     | 10    | 11  |  |

|                  | 4       | 4                  | 5     | 6     | 7   |  |

| Lower<br>Address | 0       | 0                  | 1     | 2     | 3   |  |

Figure 1-4 Big-Endian Byte Ordering

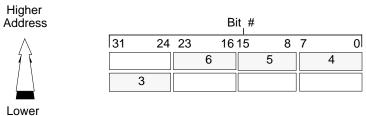

When configured as a little-endian system, byte 0 is always the least-significant (rightmost) byte, which is compatible with iAPX<sup>®</sup> x86 and DEC VAX<sup>®</sup> conventions. Figure 1-5 shows this configuration.

| Higher           | Word            | Bit <sub>1</sub> # |       |      |     |  |

|------------------|-----------------|--------------------|-------|------|-----|--|

| Address          | Word<br>Address | 31 24              | 23 16 | 15 8 | 7 0 |  |

| $\bigwedge$      | 12              | 15                 | 14    | 13   | 12  |  |

| 1                | 8               | 11                 | 10    | 9    | 8   |  |

|                  | 4               | 7                  | 6     | 5    | 4   |  |

| Lower<br>Address | 0               | 3                  | 2     | 1    | 0   |  |

Figure 1-5 Little-Endian Byte Ordering

In this text, bit 0 is always the least-significant (rightmost) bit; thus, bit designations are always little-endian (although no instructions explicitly designate bit positions within words).

Figures 1-6 and 1-7 show little-endian and big-endian byte ordering in doublewords.

Figure 1-6 Little-Endian Data in a Doubleword

Figure 1-7 Big-Endian Data in a Doubleword

The CPU uses byte addressing for halfword, word, and doubleword accesses with the following alignment constraints:

- Halfword accesses must be aligned on an even byte boundary (0, 2, 4...).

- Word accesses must be aligned on a byte boundary divisible by four (0, 4, 8...).

- Doubleword accesses must be aligned on a byte boundary divisible by eight (0, 8, 16...).

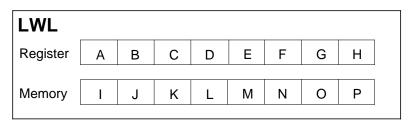

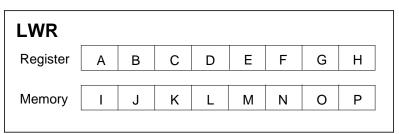

The following special instructions load and store words that are not aligned on 4-byte (word) or 8-word (doubleword) boundaries:

| LWL | LWR | SWL | SWR |

|-----|-----|-----|-----|

| LDL | LDR | SDL | SDR |

These instructions are used in pairs to provide addressing of misaligned words. Addressing misaligned data incurs one additional instruction cycle over that required for addressing aligned data.

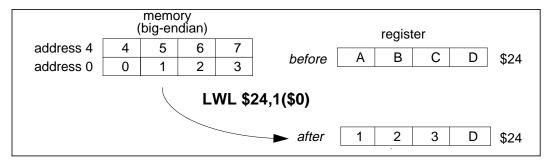

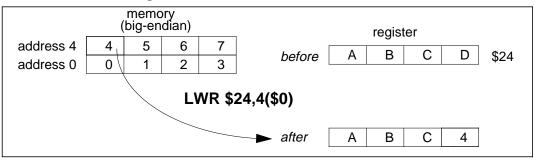

Figures 1-8 and 1-9 show the access of a misaligned word that has byte address 3.

Higher Address

| 5 |      |      | Bit <sub> </sub> # |    |     |

|---|------|------|--------------------|----|-----|

|   | 31 2 | 4 23 | 16 15              | 87 | 7 0 |

|   | 4    | 5    | 6                  | ;  |     |

|   |      |      |                    |    | 3   |

Lower Address

Figure 1-8 Big-Endian Misaligned Word Addressing

Lower Address

Figure 1-9 Little-Endian Misaligned Word Addressing

MIPS R4000 Microprocessor User's Manual

# **Coprocessors (CP0-CP2)**

The MIPS ISA defines three coprocessors (designated CP0 through CP2):

- Coprocessor 0 (**CP0**) is incorporated on the CPU chip and supports the virtual memory system and exception handling. CP0 is also referred to as the *System Control Coprocessor*.

- Coprocessor 1 (**CP1**) is reserved for the on-chip, floating-point coprocessor, the FPU.

- Coprocessor 2 (CP2) is reserved for future definition by MIPS.

CP0 and CP1 are described in the sections that follow.

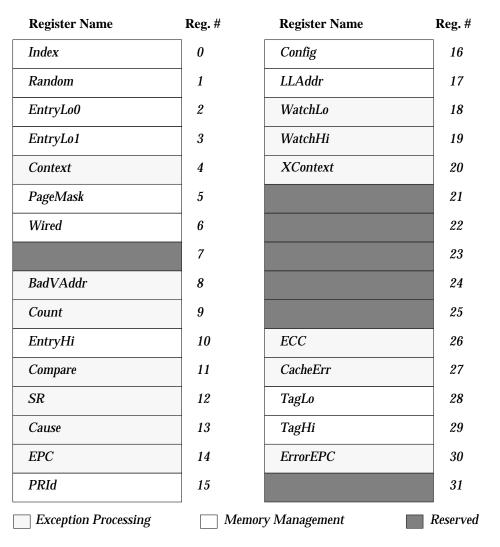

## System Control Coprocessor, CP0

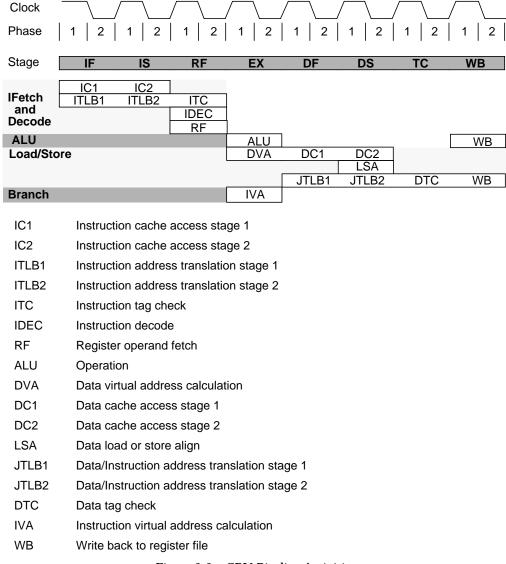

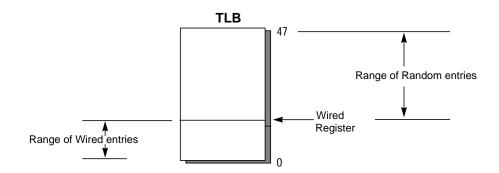

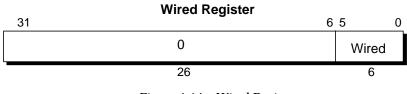

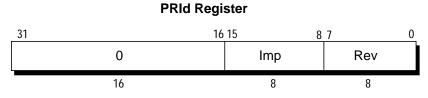

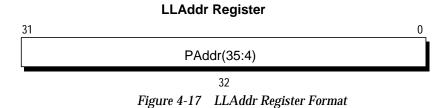

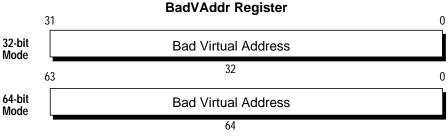

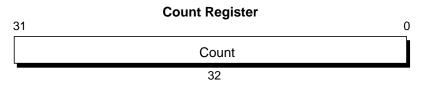

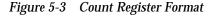

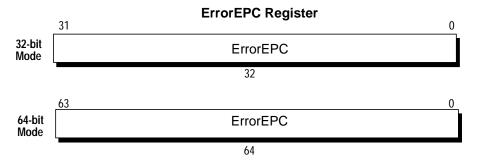

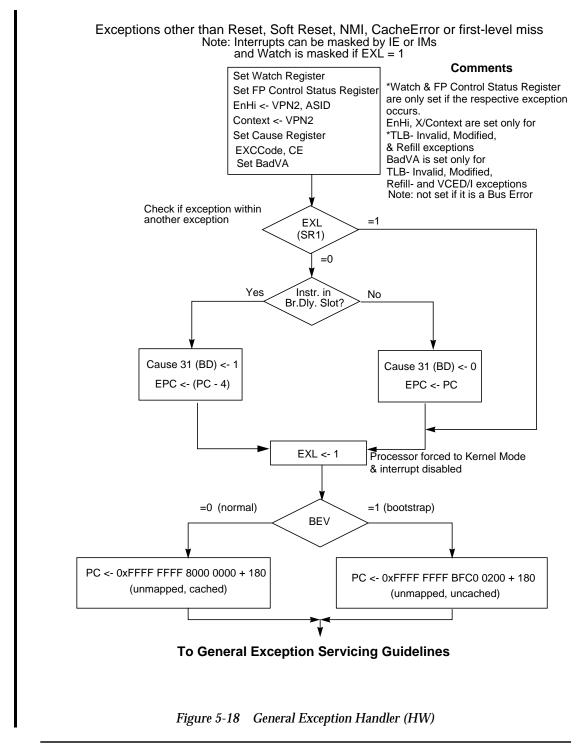

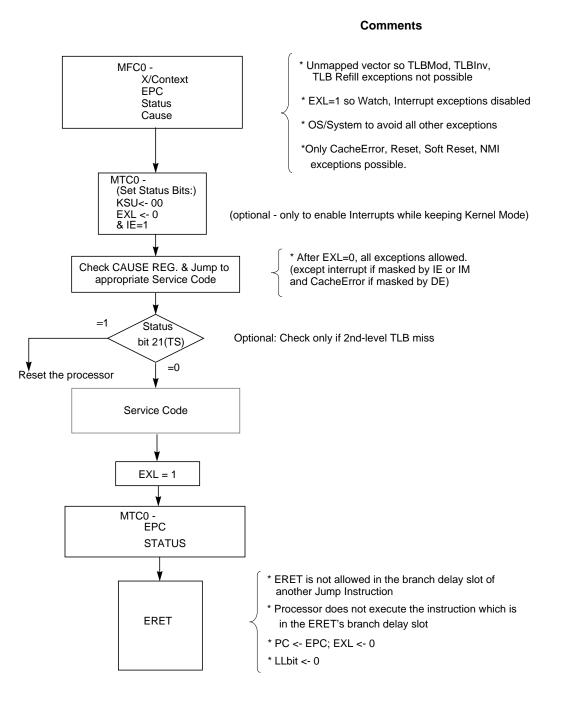

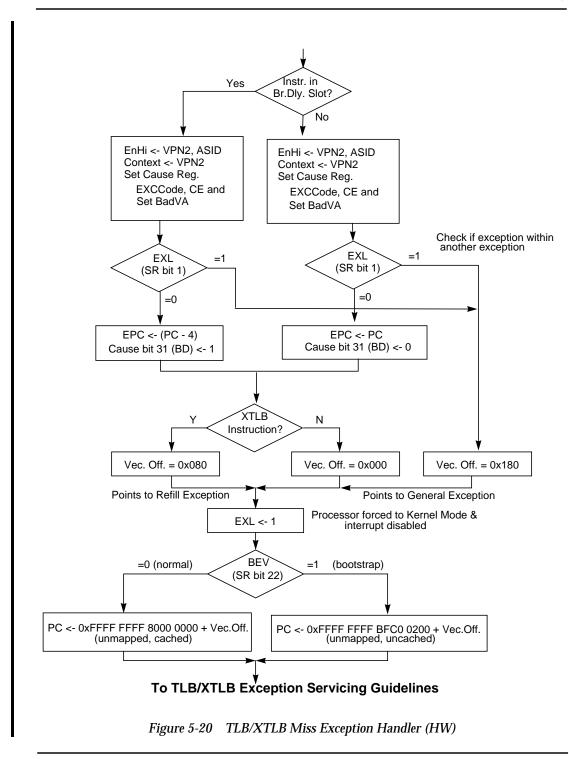

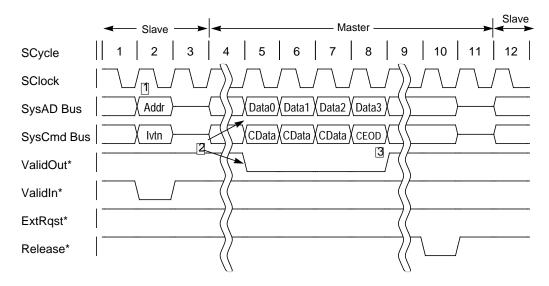

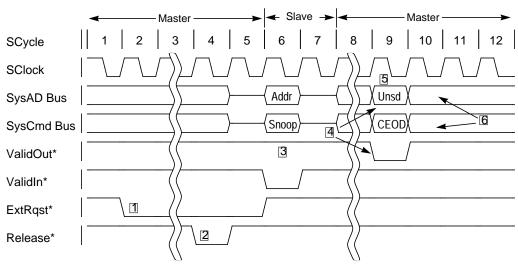

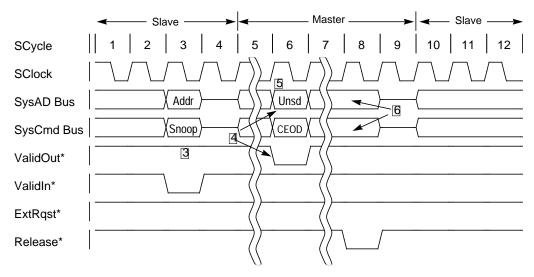

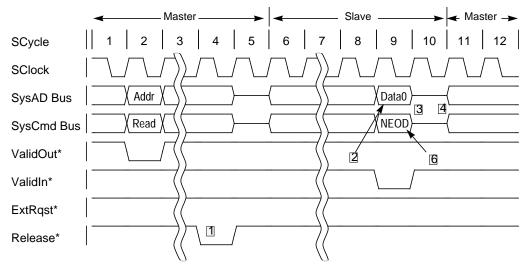

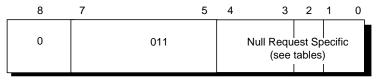

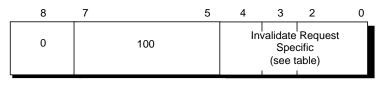

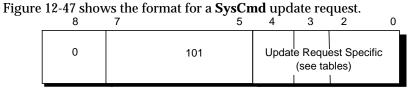

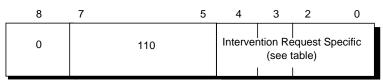

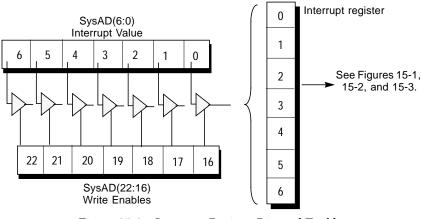

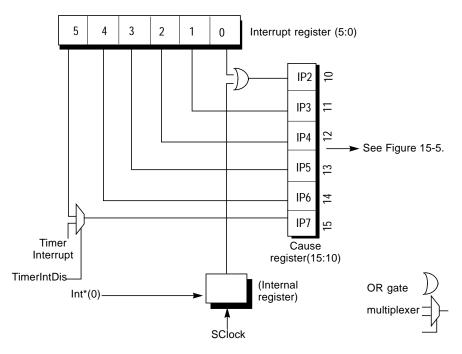

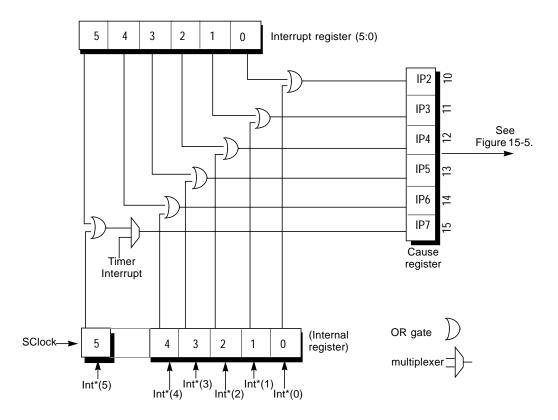

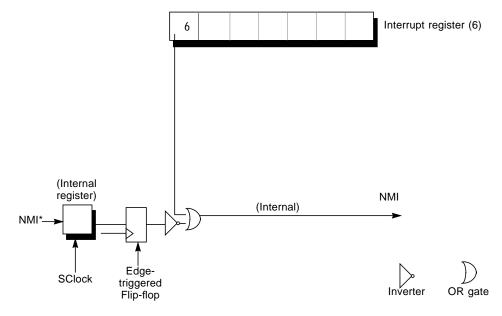

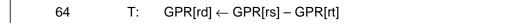

CP0 translates virtual addresses into physical addresses and manages exceptions and transitions between kernel, supervisor, and user states. CP0 also controls the cache subsystem, as well as providing diagnostic control and error recovery facilities.